Light Emitting Diode Controller (LEDC)

Introduction

The pseudo I2C only has Tx function and does not require slave reply ACK and slave address confirmation functions.

Design Implementation

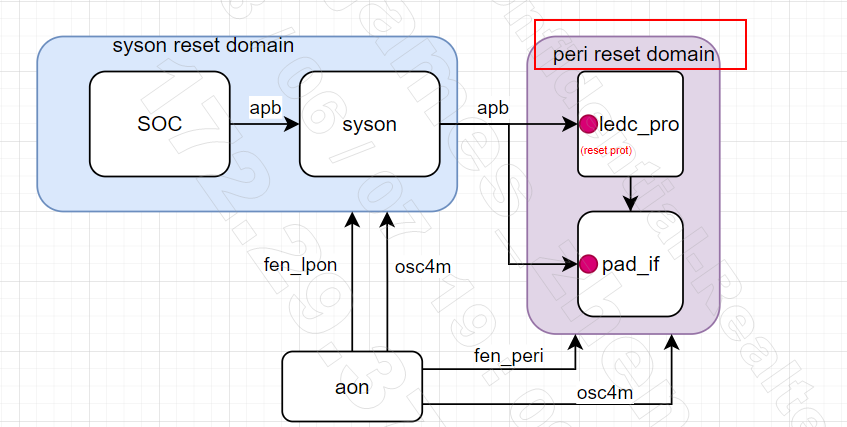

Reset Domain

Ledc_Pro and pad ctrl belong to the newly added peri reset domain in the AON area. The APB interface adds the reset protect function, and the power domain is placed in the Syson area. This design can achieve that the IP will not be reset by the system, but the software can force a reset by setting aon register.

led_pseudo_i2c

Features

Two-wire I2C serial interface – consisting of a serial data line (SDA) and a serial clock (SCL).

Supports speeds of 100K, 400K, and 1M.

Maximum size of 127 bytes when operating in pseudo I2C mode.

Pseudo I2C is used only as a master and does not require ACK/NACK signals.

The engine and pad are located in the AON (Always-On) area and do not lose power during software/watchdog/system resets. The power domain belongs to the SYSON (System-On) area.

I2C Timing

Start Signal: It is recommended to maintain an interval of at least 100ns between the data falling edge and the clock falling edge.

Stop Signal: It is recommended to maintain an interval of at least 100ns between the data rising edge and the clock rising edge.

There should be a minimum of 1us interval between the previous stop signal and the next start signal.

The DATA signal should transition after 250ns following the CLK signal’s falling edge.

Function

State Name |

Description |

|---|---|

CTL_IDLE |

idle state, when r_i2c_tx_start=1, state jump to CTL_START |

CTL_START |

start state, gen start signal, set SDA=0, SCLK =1, when div_cnt==r_i2c_clk_div*2-1, state jump to CTL_WORK |

CTL_WORK |

work state, gen SCLK/SDA and output, when gen all data, state jump to CTL_STOP |

CTL_STOP |

stop state, gen stop signal, set SDA=0, SCLK=1, when div_cnt==r_i2c_clk_div*2-1, state jump to CTL_IDLE |

IDLE State: The circuit is not operational, and SCLK/SDA remains at a logic high level.

START State: Upon receiving the software start signal, r_i2c_tx_status is pulled low, and div_cnt starts counting. The count value is set to r_i2c_clk_div2-1, with r_i2c_clk_div having a minimum value of 2. SDA is immediately pulled low, and SCLK is lowered after a delay of r_i2c_clk_div2-1 cycles, generating the start flag.

After div_cnt completes one cycle, the first psedu_fifo_read signal is generated, reading 1 byte of data from the LED buffer.

WORK State: Based on the 1-byte data read from the LED buffer and the clock division factor, the corresponding SCLK and SDA signals are generated. After pushing each byte of data, a new psedu_fifo_read signal is generated to read the next 1-byte of data until the specified length of data is read from the register.

STOP State: After reading all the data, SCLK is raised, and once div_cnt completes one cycle, SDA is raised, generating the stop flag. The system then enters the IDLE state, and r_i2c_tx_status is set to high.

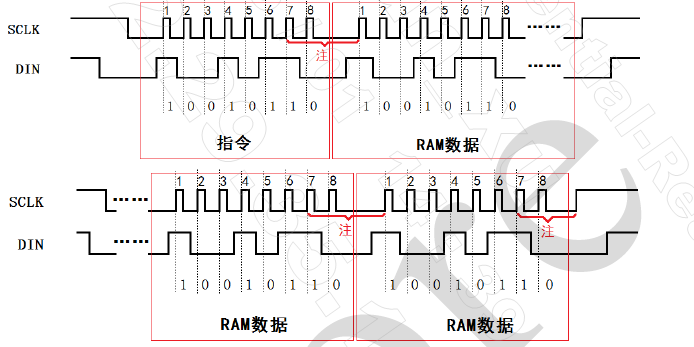

RAM Structure

The architecture of RAM is show below. The total size is 256 bytes, including 128 bytes LEDC register, 64 bytes RAM0 and 64 bytes RAM1. SW can only write and clear the block of RAM that HW is not used. When SW needs to write the RAM, it’s better to read registers to know which block of RAM that HW is used.

Operation Flow

Pseudo I2C

Read r_i2c_tx_status 0x08[6] to determine the current status of the I2C operation. If it’s 1, it indicates idle and can be operated

Write r_psedo_i2c_en 0x08[7]=1 to enable the I2C function.

Write 0x10[31:0]=0xa5a5a5a5 to disable register protection.

Write a certain quantity of 8-bit data to RAM and set r_i2c_data_num 0x08[14:8] to the number of data written to RAM. Also, write r_i2c_clk_div 0x08[5:0] to configure the clock divider, with a minimum value of 2.

First, write 0x0c[31:0]=0x69696969, then write 0x0c[31:0]=0x96969696. Trigger the hardware to read data from RAM and display it. Also, set r_seq_pass_flag 0x00[20] to 1, indicating that the sequence is correct. Clear it after reading the corresponding register once.

Write 0x10[31:0] with a non-0xa5a5a5a5 value to enable register protection.

The I2C enters the working state, r_i2c_status is set to 0. When all data is displayed, r_i2c_status is set to 1, and it returns to idle.

Registers

Base Address: 0x41105000

Name |

Address offset |

Access |

Description |

|---|---|---|---|

000h |

R/W |

||

004h |

R/W |

||

008h |

R/W |

||

00Ch |

R/W |

||

010h |

R/W |

||

014h |

R/W |

||

018h |

R/W |

||

01Ch |

R/W |

||

020h |

R/W |

||

024h |

R/W |

||

030h |

R/W |

||

0F0h |

R/W |

||

0F4h |

R/W |

REG_LEDC_CTRL_REG

Name : LEDC Control Register

Size : 32

Address offset : 000h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:29 |

RSVD |

R |

- |

Reserved |

28:16 |

TOTAL_DATA_LENGTH |

R/W |

0x0 |

Total length of transfer data, range from 1 to 8K (unit: 32 bits, only low 24-bit is valid). Actual transfer package is TOTAL_DATA_LENGTH+1. The field is recommended to an integer multiple of (LED_NUM+ 1). Note If TOTAL_DATA_LENGTH is greater than (LED_NUM+1) but not integer multiple, the last frame of data will be transfer ed less than (LED_NUM+1). |

15:11 |

RSVD |

R |

- |

Reserved |

10 |

RESET_LED_EN |

R/W |

0x0 |

Write operation: When software writes 1 to this bit, LEDC FSM turns to CPU_RE SET_LED state, and CPU triggers LEDC to transfer a reset to LED. Note Only when LEDC is in IDLE state, FSM can turn to CPU_RESE T_LED state.

Read operation:

|

9 |

LED_POLARITY |

R/W |

0x0 |

LED DI level when free.

|

8:6 |

LED_RGB_MODE |

R/W |

0x0 |

LEDC inputs 24 bits data package in order of {byte2, byte1, byte0}.

|

5 |

LED_MSB_TOP |

R/W |

0x1 |

Source RGB data format.

|

4 |

LED_MSB_BYTE2 |

R/W |

0x1 |

LEDC outputs 24 bits data package in order of {byte2, byte1, byte0}.

|

3 |

LED_MSB_BYTE1 |

R/W |

0x1 |

LEDC outputs 24 bits data package in order of {byte2, byte1, byte0}.

|

2 |

LED_MSB_BYTE0 |

R/W |

0x1 |

LEDC outputs 24 bits data package in order of {byte2, byte1, byte0}.

|

1 |

LEDC_SOFT_RESET |

R/W |

0x0 |

LEDC software reset. If software writes 1 to this bit, the next cycle hardware wi ll clear LEDC_SOFT_RESET to 0, which will generate a pulse. LEDC soft reset includes all interrupt status register, the control state machine returns to the IDLE state, LEDC FIFO r ead and write point is cleared to 0, LEDC interrupt is clear ed. The related registers are as below:

Other registers remain unchanged. |

0 |

LEDC_EN |

R/W |

0x0 |

LEDC enable bit.

This bit enable indicates that LEDC can be started when LEDC data has finished transmission, or this bit is cleared to 0 by hardware when software sets LEDC_SOFT_RESET. Software clearing LEDC_EN when LEDC FSM is not IDLE doesn’t affect data transfer. |

REG_LED_T01_TIMING_CTRL_REG

Name : LED Timing Control Register

Size : 32

Address offset : 004h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:24 |

T1H_CNT |

R/W |

0x20 |

LED modulate logical “1” high level time (T1H_TIME). Unit: cycle (40MHz), T1H_TIME = 25ns * T1H_CNT, where T1H_CN T>0 T1H_TIME default value is 800ns. |

23:16 |

T1L_CNT |

R/W |

0xc |

LED modulate logical “1” low level time. Unit: cycle (40MHz), T1L_TIME = 25ns *T1L_CNT, where T1L_CNT >0 T1L_TIME default value is 300ns. |

15:8 |

T0H_CNT |

R/W |

0xc |

LED modulate logical “0” high level time. Unit: cycle (40MHz), T0H_TIME = 25ns * T0H_CNT, where T0H_CN T>0 T0H_TIME default value is 300ns. |

7:0 |

T0L_CNT |

R/W |

0x20 |

LED modulate logical “0” low level time. Unit: cycle (40MHz), T0L_TIME = 25ns *T0L_CNT, where T0L_CNT >0 T0L_TIME default value is 800ns. |

REG_LEDC_DATA_FINISH_CNT_REG

Name : LEDC Data Finish Register

Size : 32

Address offset : 008h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

RSVD |

R |

- |

Reserved |

30:16 |

LED_WAIT_DATA_TIME |

R/W |

0x2edf |

The time that internal FIFO of LEDC is waiting for data. The default value is 300us by default. To avoid to insert LED RESET between two-pixel data, hardwa re will send WAITDATA_TIMEOUT_INT when wait_time>= min(RESET _TIME, LED_WAIT_DATA_TIME). The adjust range is from 25ns ~ 819us, LED_WAIT_DATA_TIME = 25ns *(N+1) where N is from 0 to 0x7FFF. When the setting time is exceeded, LEDC will send WAITDATA_T IMEOUT_INT interrupt. Under this abnormal situation, softwar e should reset LEDC. |

15:13 |

RSVD |

R |

- |

Reserved |

12:0 |

LED_DATA_FINISH_CNT |

R |

0x0 |

The total LED data have been sent (range: 0 ~ 8K). When LEDC transfer finishes normally, this register is clear ed by hardware when generating trans_finish_int. Software kn ows LED_DATA_FINISH_CNT equal to TOTAL_DATA_LENGTH. When LEDC transfer interrupt abnormally, this register will be cleared to 0 by software by setting LEDC_SOFT_RESET. |

REG_LED_RESET_TIMING_CTRL_REG

Name : LED Reset Timing Control Register

Size : 32

Address offset : 00Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:30 |

RSVD |

R |

- |

Reserved |

29:16 |

RESET_TIME |

R/W |

0x2edf |

Reset time control of LED lamp. The default reset time is 300us. The adjust range is from 25ns to 409.6us. RESET_TIME = 25ns *(N+1) where N is from 0 to 0x3FFF. |

15:10 |

RSVD |

R |

- |

Reserved |

9:0 |

LED_NUM |

R/W |

0x0 |

The number of external LED lamp. Maximum up to 1024. The default value is 0, which indicate that 1 LED lamp is co nnected. The range is from 0 to 1023. |

REG_LEDC_WAIT_TIME0_CTRL_REG

Name : LED Wait Time 0 Control Register

Size : 32

Address offset : 010h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:10 |

RSVD |

R |

- |

Reserved |

9 |

WAIT_TIME0_EN |

R/W |

0 |

Wait time0 enable. When setting this bit, the controller automatically inserts waiting time before next LED package data.

|

8:0 |

TOTAL_WAIT_TIME0 |

R/W |

0x1FF |

Waiting time between 2 LED data, and LEDC outputs Low level during waiting time0. The adjust range is from 25ns to 12.5us, WAIT_TIME0 = 25ns*( N+1), where N is from 0 to 0x1FF. |

REG_LEDC_WAIT_TIME1_CTRL_REG

Name : LED Wait Time 1 Control Register

Size : 32

Address offset : 014h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

WAIT_TIME1_EN |

R/W |

0 |

Wait time1 enable. When setting this bit, the controller automatically inserts waiting time before next LED frame data.

|

30:0 |

TOTAL_WAIT_TIME1 |

R/W |

0x1FFFFFF |

Waiting time between 2 frame data, and LEDC outputs Low leve l during waiting time1. The adjust range is from 25ns to 53s, WAIT_TIME0 = 25ns*(N+1 ), where N is from 0 to 0x7FFFFFFF. |

REG_LEDC_DATA_REG

Name : LED Data Register

Size : 32

Address offset : 018h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:24 |

RSVD |

R |

- |

Reserved |

23:0 |

LEDC_DATA |

R/W |

0 |

LEDC display data, the lower 24-bit is valid. Writ this register means push data to LEDC FIFO. Register LEDC_EN toggling from 0 to 1 will clear LEDC FIFO. Thus, only data pushed when LEDC_EN=1 will be send to LED. |

REG_LEDC_DMA_CTRL_REG

Name : LED DMA Control Register

Size : 32

Address offset : 01Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:6 |

RSVD |

R |

- |

Reserved |

5 |

LEDC_DMA_EN |

R/W |

0x1 |

LEDC DMA request enable.

|

4:0 |

LEDC_FIFO_TRIG_LEVEL |

R/W |

0xF |

The remaining space of internal FIFO in LEDC. When the remain space of internal LEDC FIFO is larger than L EDC_FIFO_TRIG_LEVEL, a DMA request or cpu_req_int will gener ate. Note The default value is 15. The adjust range is from 0 to 31 , and the recommended configuration is 7 or 15. |

REG_LED_INTERRUPT_CTRL_REG

Name : LED Interrupt Control Register

Size : 32

Address offset : 020h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:5 |

RSVD |

R |

- |

Reserved |

4 |

GLOBAL_INT_EN |

R/W |

0 |

Global interrupt enable.

|

3 |

FIFO_OVERFLOW_INT_EN |

R/W |

0 |

FIFO overflow interrupt enable. When the data written by software is more than internal FIFO level of LEDC, LEDC is in data loss state.

|

2 |

WAITDATA_TIMEOUT_INT_EN |

R/W |

0 |

The internal FIFO in LEDC can’t get data after the LED_WAIT_ DATA_TIME, the interrupt will be enable.

|

1 |

FIFO_CPUREQ_INT_EN |

R/W |

0 |

FIFO request CPU data interrupt enable.

|

0 |

LED_TRANS_FINISH_INT_EN |

R/W |

0 |

Data transmission complete interrupt enable.

|

REG_LED_INT_STS_REG

Name : LED FIFO Status Register

Size : 32

Address offset : 024h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:18 |

RSVD |

R |

- |

Reserved |

17 |

FIFO_EMPTY |

R |

0x1 |

FIFO empty status flag. When LEDC_EN is 0, FIFO_EMPTY equal 1. This flush residual d ata when LED_NUM is not integer multiples of burst length. |

16 |

FIFO_FULL |

R |

0 |

FIFO full status flag. |

15:4 |

RSVD |

R |

- |

Reserved |

3 |

FIFO_OVERFLOW_INT |

R/W |

0 |

FIFO overflow interrupt Clear 0 when software set LEDC_SOFT_RESET. The data written by external is more than the maximum storag e space of LEDC FIFO. At this time, software needs to deal w ith the abnormal situation. LEDC performs soft_reset operati on to refresh all data.

|

2 |

WAITDATA_TIMEOUT_INT |

R/W |

0 |

Before transfer a frame: When the internal FIFO in LEDC can’ t get data after the LED_WAIT_DATA_TIME, this bit is set. During transfer of a frame (between two pixel of data): to a void insert LED RESET between two pixel data, hardware will send WAITDATA_TIMEOUT_INT when wait_time>= min(RESET_TIME,LE D_WAIT_DATA_TIME). Clear 0 when software sets LEDC_SOFT_RESET. When new data arrives at WAIT_DATA state, LEDC will continue sending data. Note Software should note that if the waiting time exceeds the operation of reset time, LEDC may enter refresh state, ne w data has not been sent.

|

1 |

FIFO_CPUREQ_INT |

R/W |

0 |

When FIFO data available is less than the threshold left, th e interrupt is reported to CPU. Clear 0 when software sets LEDC_SOFT_RESET.

Note When getting FIFO_CPUREQ_INT, CPU writes 1 data to LEDC B uffer. It is inefficiently compared to DMA mode. |

0 |

LED_TRANS_FINISH_INT |

R/W |

0 |

When the data configured as TOTAL_DATA_LENGTH has been trans ferred complete, this bit is set. Clear 0 when software sets LEDC_SOFT_RESET.

|

REG_LEDC_DEBUG_SEL_REG

Name : LED Debug Select Register

Size : 32

Address offset : 030h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:9 |

RSVD |

R |

- |

Reserved |

8:7 |

LEDC_DEBUG_SEL_DRIVE |

R/W |

0 |

Drive module debug out select. |

6:3 |

LEDC_DEBUG_SEL_FIFO |

R/W |

0 |

FIFO module debug out select. [6:5]: select debug_data of ledc_txfifo, valid range is 0 or 1. [4:3]: select output data byte when bit[6:5] is 0.

|

2:0 |

LEDC_DEBUG_SEL_TOP |

R/W |

0 |

LEDC top module debug out select. |

REG_DUMMY_F0

Name : Dummy register

Size : 32

Address offset : 0F0h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

DUMMY |

R/W |

32’hffffffff |

Dummy register |

REG_DUMMY_F4

Name : Dummy register

Size : 32

Address offset : 0F4h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

DUMMY |

R/W |

32’h0 |

Dummy register |

Base Address: 0x41015000

Name |

Address offset |

Access |

Description |

|---|---|---|---|

000h |

R/W |

||

004h |

R/W |

||

008h |

R/W |

||

00Ch |

R/W |

||

010h |

R/W |

||

014h |

R/W |

||

018h |

R/W |

||

01Ch |

R/W |

||

020h |

R/W |

||

024h |

R/W |

||

030h |

R/W |

||

0F0h |

R/W |

||

0F4h |

R/W |

REG_LEDC_CTRL_REG

Name : LEDC Control Register

Size : 32

Address offset : 000h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:29 |

RSVD |

R |

- |

Reserved |

28:16 |

TOTAL_DATA_LENGTH |

R/W |

0x0 |

Total length of transfer data, range from 1 to 8K (unit: 32 bits, only low 24-bit is valid). Actual transfer package is TOTAL_DATA_LENGTH+1. The field is recommended to an integer multiple of (LED_NUM+ 1). Note If TOTAL_DATA_LENGTH is greater than (LED_NUM+1) but not integer multiple, the last frame of data will be transfer red less than (LED_NUM+1). |

15:11 |

RSVD |

R |

- |

Reserved |

10 |

RESET_LED_EN |

R/W |

0x0 |

Write operation: When software writes 1 to this bit, LEDC FSM turns to CPU_RE SET_LED state, and CPU triggers LEDC to transfer a reset to LED. Note Only when LEDC is in IDLE state, can FSM turn to CPU_RES ET_LED state.

Read operation:

|

9 |

LED_POLARITY |

R/W |

0x0 |

LED DI level when free.

|

8:6 |

LED_RGB_MODE |

R/W |

0x0 |

LEDC inputs 24 bits data package in order of {byte2, byte1, byte0}.

|

5 |

LED_MSB_TOP |

R/W |

0x1 |

Source RGB data format.

|

4 |

LED_MSB_BYTE2 |

R/W |

0x1 |

LEDC outputs 24 bits data package in order of {byte2, byte1, byte0};

|

3 |

LED_MSB_BYTE1 |

R/W |

0x1 |

LEDC outputs 24 bits data package in order of {byte2, byte1, byte0};

|

2 |

LED_MSB_BYTE0 |

R/W |

0x1 |

LEDC outputs 24 bits data package in order of {byte2, byte1, byte0};

|

1 |

LEDC_SOFT_RESET |

R/W |

0x0 |

LEDC software reset. If software writes 1 to this bit, the next cycle hardware wi ll clear LEDC_SOFT_RESET to 0, which will generate a pulse. LEDC soft reset includes all interrupt status register, the control state machine returns to the IDLE state, LEDC FIFO r ead and write point is cleared to 0, LEDC interrupt is clear ed. The related registers are as below:

Other registers remain unchanged. |

0 |

LEDC_EN |

R/W |

0x0 |

LEDC enable bit.

This bit enable indicates that LEDC can be started when LEDC data has finished transmission, or this bit is cleared to 0 by hardware when software sets LEDC_SOFT_RESET. Software clearing LEDC_EN when LEDC FSM is not IDLE don’t af fect data transfer. |

REG_LED_T01_TIMING_CTRL_REG

Name : LED Timing Control Register

Size : 32

Address offset : 004h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:24 |

T1H_CNT |

R/W |

0x20 |

LED modulate logical “1” high level time (T1H_TIME). Unit: cycle (40MHz), T1H_TIME = 25ns * T1H_CNT, where T1H_CN T>0 T1H_TIME default value is 800ns. |

23:16 |

T1L_CNT |

R/W |

0xc |

LED modulate logical “1” low level time. Unit: cycle (40MHz), T1L_TIME = 25ns *T1L_CNT, where T1L_CNT >0 T1L_TIME default value is 300ns. |

15:8 |

T0H_CNT |

R/W |

0xc |

LED modulate logical “0” high level time. Unit: cycle (40MHz), T0H_TIME = 25ns * T0H_CNT, where T0H_CN T>0 T0H_TIME default value is 300ns. |

7:0 |

T0L_CNT |

R/W |

0x20 |

LED modulate logical “0” low level time. Unit: cycle (40MHz), T0L_TIME = 25ns *T0L_CNT, where T0L_CNT >0 T0L_TIME default value is 800ns. |

REG_LEDC_DATA_FINISH_CNT_REG

Name : LEDC Data Finish Register

Size : 32

Address offset : 008h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

RSVD |

R |

- |

Reserved |

30:16 |

LED_WAIT_DATA_TIME |

R/W |

0x2edf |

The time that internal FIFO of LEDC is waiting for data. The default value is 300us by default. To avoid to insert LED RESET between two-pixel data, hardwa re will send WAITDATA_TIMEOUT_INT when wait_time>= min (RESE T_TIME, LED_WAIT_DATA_TIME). The adjust range is from 25ns ~ 819us, LED_WAIT_DATA_TIME = 25ns *(N+1) where N is from 0 to 0x7FFF. When the setting time is exceeded, LEDC will send WAITDATA_T IMEOUT_INT interrupt. Under this abnormal situation, softwar e should reset LEDC. |

15:13 |

RSVD |

R |

- |

Reserved |

12:0 |

LED_DATA_FINISH_CNT |

R |

0x0 |

The total LED data have been sent. (range: 0 ~ 8K). When LEDC transfer finishes normally, this register is clear ed by hardware when generating trans_finish_int. Software kn ows LED_DATA_FINISH_CNT equal to TOTAL_DATA_LENGTH. When LEDC transfers interrupt abnormally, this register will be cleared to 0 by software by setting LEDC_SOFT_RESET. |

REG_LED_RESET_TIMING_CTRL_REG

Name : LED Reset Timing Control Register

Size : 32

Address offset : 00Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:30 |

RSVD |

R |

- |

Reserved |

29:16 |

RESET_TIME |

R/W |

0x2edf |

Reset time control of LED lamp. The default reset time is 300us. The adjust range is from 25ns to 409.6us. RESET_TIME = 25ns *(N+1) where N is from 0 to 0x3FFF. |

15:10 |

RSVD |

R |

- |

Reserved |

9:0 |

LED_NUM |

R/W |

0x0 |

The number of external LED lamp. Maximum up to 1024. The default value is 0, which indicate that 1 LED lamp is co nnected. The range is from 0 to 1023. |

REG_LEDC_WAIT_TIME0_CTRL_REG

Name : LED Wait Time 0 Control Register

Size : 32

Address offset : 010h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:10 |

RSVD |

R |

- |

Reserved |

9 |

WAIT_TIME0_EN |

R/W |

0 |

Wait time0 enable. When set this bit, the controller automatically inserts wait ing time before next LED package data.

|

8:0 |

TOTAL_WAIT_TIME0 |

R/W |

0x1FF |

Waiting time between 2 LED data, and LEDC outputs Low level during waiting time0. The adjust range is from 25ns to 12.5us, WAIT_TIME0 = 25ns * (N+1) where N is from 0 to 0x1FF. |

REG_LEDC_WAIT_TIME1_CTRL_REG

Name : LED Wait Time 1 Control Register

Size : 32

Address offset : 014h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

WAIT_TIME1_EN |

R/W |

0 |

Wait time1 enable. When set this bit, the controller automatically inserts wait ing time before next LED frame data.

|

30:0 |

TOTAL_WAIT_TIME1 |

R/W |

0x1FFFFFF |

Waiting time between 2 frame data, and LEDC outputs Low leve l during waiting time1. The adjust range is from 25ns to 53s, WAIT_TIME0 = 25ns *(N+ 1) where N is from 0 to 0x7FFFFFFF. |

REG_LEDC_DATA_REG

Name : LED Data Register

Size : 32

Address offset : 018h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:24 |

RSVD |

R |

- |

Reserved |

23:0 |

LEDC_DATA |

R/W |

0 |

LEDC display data, the lower 24-bit is valid. Writ this register means push data to LEDC FIFO. Register LEDC_EN toggles from 0 to 1 will clear LEDC FIFO. T hus, only data pushed when LEDC_EN=1 will be send to LED. |

REG_LEDC_DMA_CTRL_REG

Name : LED DMA Control Register

Size : 32

Address offset : 01Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:6 |

RSVD |

R |

- |

Reserved |

5 |

LEDC_DMA_EN |

R/W |

0x1 |

LEDC DMA request enable.

|

4:0 |

LEDC_FIFO_TRIG_LEVEL |

R/W |

0xF |

The remaining space of internal FIFO in LEDC. When the remain space of internal LEDC FIFO is larger than L EDC_FIFO_TRIG_LEVEL, a DMA request or cpu_req_int will gener ate. Note The default value is 15. The adjust range is from 0 to 31 , and the recommended configuration is 7 or 15. |

REG_LED_INTERRUPT_CTRL_REG

Name : LED Interrupt Control Register

Size : 32

Address offset : 020h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:5 |

RSVD |

R |

- |

Reserved |

4 |

GLOBAL_INT_EN |

R/W |

0 |

Global interrupt enable.

|

3 |

FIFO_OVERFLOW_INT_EN |

R/W |

0 |

FIFO overflow interrupt enable. When the data written by software is more than internal FIFO level of LEDC, LEDC is in data loss state.

|

2 |

WAITDATA_TIMEOUT_INT_EN |

R/W |

0 |

The internal FIFO in LEDC can’t get data after the LED_WAIT_ DATA_TIME, the interrupt will be enable.

|

1 |

FIFO_CPUREQ_INT_EN |

R/W |

0 |

FIFO request CPU data interrupt enable.

|

0 |

LED_TRANS_FINISH_INT_EN |

R/W |

0 |

Data transmission complete interrupt enable.

|

REG_LED_INT_STS_REG

Name : LED Interrupt Status Register

Size : 32

Address offset : 024h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:18 |

RSVD |

R |

- |

Reserved |

17 |

FIFO_EMPTY |

R |

0x1 |

FIFO empty status flag. When LEDC_EN is 0, FIFO_EMPTY equal 1. This flush residual d ata when LED_NUM is not integer multiples of burst length. |

16 |

FIFO_FULL |

R |

0 |

FIFO full status flag. |

15:4 |

RSVD |

R |

- |

Reserved |

3 |

FIFO_OVERFLOW_INT |

R/W |

0 |

FIFO overflow interrupt Clear 0 when software set LEDC_SOFT_RESET. The data written by external is more than the maximum storag e space of LEDC FIFO. At this time, software needs to deal w ith the abnormal situation. LEDC performs soft_reset operati on to refresh all data.

|

2 |

WAITDATA_TIMEOUT_INT |

R/W |

0 |

Before transfer a frame: When the internal FIFO in LEDC can’ t get data after the LED_WAIT_DATA_TIME, this bit is set. During transfer of a frame (between two pixel of data): to a void insert LED RESET between two pixel data, hardware will send WAITDATA_TIMEOUT_INT when wait_time>= min(RESET_TIME,LE D_WAIT_DATA_TIME). Clear 0 when software sets LEDC_SOFT_RESET. When new data arrives at WAIT_DATA state, LEDC will continue sending data. Note Software should note that if the waiting time exceeds the operation of reset time, LEDC may enter refresh state, ne w data has not been sent.

|

1 |

FIFO_CPUREQ_INT |

R/W |

0 |

When FIFO data available is less than the threshold left, th e interrupt is reported to CPU. Clear 0 when software sets LEDC_SOFT_RESET.

Note When getting FIFO_CPUREQ_INT, CPU writes 1 data to LEDC B uffer. It is inefficiently compared to DMA mode. |

0 |

LED_TRANS_FINISH_INT |

R/W |

0 |

When the data configured as TOTAL_DATA_LENGTH has been trans ferred complete, this bit is set. Clear 0 when software sets LEDC_SOFT_RESET.

|

REG_LEDC_DEBUG_SEL_REG

Name : LED Debug Selection Register

Size : 32

Address offset : 030h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:9 |

RSVD |

R |

- |

Reserved |

8:7 |

LEDC_DEBUG_SEL_DRIVE |

R/W |

0 |

Drive module debug out selection. |

6:3 |

LEDC_DEBUG_SEL_FIFO |

R/W |

0 |

FIFO module debug out select. [6:5]: select debug_data of ledc_txfifo, valid range is 0 or 1 [4:3]: select output data byte when [6:5] is 0.

|

2:0 |

LEDC_DEBUG_SEL_TOP |

R/W |

0 |

LEDC top module debug out select. |

REG_DUMMY_F0

Name : Dummy Register

Size : 32

Address offset : 0F0h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

DUMMY |

R/W |

32’hffffffff |

REG_DUMMY_F4

Name : Dummy Register

Size : 32

Address offset : 0F4h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

DUMMY |

R/W |

32’h0 |

Base Address: 0x41008000

Name |

Address offset |

Access |

Description |

|---|---|---|---|

000h |

R/W |

||

004h |

R/W |

||

008h |

R/W |

||

00Ch |

R/W |

||

010h |

R/W |

||

014h |

R/W |

||

018h |

R/W |

||

01Ch |

R/W |

||

020h |

R/W |

||

024h |

R/W |

||

030h |

R/W |

REG_LEDC_CTRL_REG

Size : 32

Address offset : 000h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:29 |

RSVD |

R |

- |

Reserved |

28:16 |

TOTAL_DATA_LENGTH |

R/W |

0x0 |

Total length of transfer data, range from 1 to 8K (unit:32 b its, only low 24-bit is valid). Actual transfer packages is TOTAL_DATA_LENGTH+1. The field is recommended to an integer multiple of (LED_NUM+ 1). Note If TOTAL_DATA_LENGTH is greater than (LED_NUM+1) but not integer multiple, the last frame of data will transfer da ta less than (LED_NUM+1). |

15:11 |

RSVD |

R |

- |

Reserved |

10 |

RESET_LED_EN |

R/W |

0x0 |

Write operation: When software writes 1 to this bit, LEDC FSM turns to CPU_RE SET_LED state, and CPU triggers LEDC to transfer a reset to LED. Note Only when LEDC is in the IDLE state, can FSM turn to CPU_ RESET_LED state.

Read operation:

|

9 |

LED_POLARITY |

R/W |

0x0 |

LED DI level when free.

|

8:6 |

LED_RGB_MODE |

R/W |

0x0 |

LEDC inputs 24 bits data pakage in order of {byte2, byte1, b yte0}.

|

5 |

LED_MSB_TOP |

R/W |

0x1 |

Source RGB data format.

|

4 |

LED_MSB_BYTE2 |

R/W |

0x1 |

LEDC outputs 24 bits data pakage in order of {byte2, byte1, byte0};

|

3 |

LED_MSB_BYTE1 |

R/W |

0x1 |

LEDC outputs 24 bits data pakage in order of {byte2, byte1, byte0};

|

2 |

LED_MSB_BYTE0 |

R/W |

0x1 |

LEDC outputs 24 bits data pakage in order of {byte2, byte1, byte0};

|

1 |

LEDC_SOFT_RESET |

R/W |

0x0 |

LEDC software reset. If software writes 1 to LEDC_SOFT_RESET, the next cycle hard ware will clear LEDC_SOFT_RESET to 0, which will generate a pulse. LEDC soft reset includes all interrupt status register, the control state machine returns to the IDLE state, LEDC FIFO r ead and write point is cleared to 0, LEDC interrupt is clear ed. The related registers are as below:

Other registers remain unchanged. |

0 |

LEDC_EN |

R/W |

0x0 |

LEDC enable bit.

This bit enable indicates that LEDC can be started when LEDC data finished transmission, or this bit is cleared to 0 by h ardware when software sets LEDC_SOFT_RESET. Software clears LEDC_EN when LEDC FSM is not IDLE don’t affe ct data transfer. |

REG_LED_T01_TIMING_CTRL_REG

Size : 32

Address offset : 004h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:24 |

T1H_CNT |

R/W |

0x20 |

LED modulate logical “1” high level time (T1H_TIME). Unit: cycle (40MHz), T1H_TIME = 25ns * T1H_CNT , where T1H_C NT>0 T1H_TIME default value is 800ns. |

23:16 |

T1L_CNT |

R/W |

0xc |

LED modulate logical “1” low level time. Unit: cycle (40MHz), T1L_TIME = 25ns *T1L_CNT, where T1L_CN T>0 T1L_TIME default value is 300ns. |

15:8 |

T0H_CNT |

R/W |

0xc |

LED modulate logical “0” hgh level time. Unit: cycle (40MHz), T0H_TIME = 25ns * T0H_CNT , where T0H_C NT>0 T0H_TIME default value is 300ns. |

7:0 |

T0L_CNT |

R/W |

0x20 |

LED modulate logical “0” low level time. Unit: cycle (40MHz), T0L_TIME = 25ns *T0L_CNT, where T0L_CNT >0 T0L_TIME default value is 800ns. |

REG_LEDC_DATA_FINISH_CNT_REG

Size : 32

Address offset : 008h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

RSVD |

R |

- |

Reserved |

30:16 |

LED_WAIT_DATA_TIME |

R/W |

0x2edf |

The time that internal FIFO of LEDC is waiting for data. The default value is 300us by default. To avoid insert LED RESET between two pixel data, hardware w ill send WAITDATA_TIMEOUT_INT when wait_time>= min (RESET_TI ME, LED_WAIT_DATA_TIME). The adjust range is from 25ns ~ 819us, LED_WAIT_DATA_TIME = 25ns *(N+1) where N is from 0 to 0x7FFF. When the setting time is exceeded, LEDC will send WAITDATA_T IMEOUT_INT interrupt. Under this abnormal situation, softwar e should reset LEDC. |

15:13 |

RSVD |

R |

- |

Reserved |

12:0 |

LED_DATA_FINISH_CNT |

R |

0x0 |

The total LED data have been sent. (range: 0 ~ 8K). When LEDC transfer finishs normally, this register is cleare d by hardware when generate trans_finish_int. Software knows LED_DATA_FINISH_CNTequals to TOTAL_DATA_LENGTH. When LEDC transfer interrupt abnormally,this register will c lear to 0 by software by setting LEDC_SOFT_RESET. |

REG_LED_RESET_TIMING_CTRL_REG

Size : 32

Address offset : 00Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:30 |

RSVD |

R |

- |

Reserved |

29:16 |

RESET_TIME |

R/W |

0x2edf |

Reset time control of LED lamp. The default reset time is 300us. The adjust range is from 25ns to 409.6us. RESET_TIME = 25ns *(N+1) where N is from 0 to 0x3FFF. |

15:10 |

RSVD |

R |

- |

Reserved |

9:0 |

LED_NUM |

R/W |

0x0 |

The number of external LED lamp. Maximum up to 1024. The default value is 0, which indicate that 1 LED lamp is co nnected. The range is from 0 to 1023. |

REG_LEDC_WAIT_TIME0_CTRL_REG

Size : 32

Address offset : 010h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:10 |

RSVD |

R |

- |

Reserved |

9 |

WAIT_TIME0_EN |

R/W |

0 |

Wait time0 enable. When set this bit, the controller automatically insert waiti ng time before next LED package data.

|

8:0 |

TOTAL_WAIT_TIME0 |

R/W |

0x1FF |

Waiting time between 2 LED data, and LEDC output Low level d uring waiting time0. The adjust range is from 25ns to 12.5us, WAIT_TIME0 = 25ns * (N+1) where N is from 0 to 0x1FF. |

REG_LEDC_WAIT_TIME1_CTRL_REG

Size : 32

Address offset : 014h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

WAIT_TIME1_EN |

R/W |

0 |

Wait time1 enable. When set this bit, the controller automatically insert waiti ng time before next LED frame data.

|

30:0 |

TOTAL_WAIT_TIME1 |

R/W |

0x1FFFFFF |

Waiting time between 2 frame data, and LEDC output Low level during waiting time1. The adjust range is from 25ns to 53s, WAIT_TIME0 = 25ns *(N+ 1) where N is from 0 to 0x7FFFFFFF. |

REG_LEDC_DATA_REG

Size : 32

Address offset : 018h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:24 |

RSVD |

R |

- |

Reserved |

23:0 |

LEDC_DATA |

R/W |

0 |

LEDC display data, the lower 24-bit is valid. Write this register means push data to LEDC FIFO. Register LEDC_EN toggle from 0->1 will clear LEDC FIFO. Thu s, only data pushed when LEDC_EN=1 will be send to LED. |

REG_LEDC_DMA_CTRL_REG

Size : 32

Address offset : 01Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:6 |

RSVD |

R |

- |

Reserved |

5 |

LEDC_DMA_EN |

R/W |

0x1 |

LEDC DMA request enable.

|

4:0 |

LEDC_FIFO_TRIG_LEVEL |

R/W |

0xF |

The remaining space of internal FIFO in LEDC When the remain space of internal LEDC FIFO is larger than L EDC_FIFO_TRIG_LEVEL,will generate dma request or cpu_req_int . Note : The default value is 15. The adjust range is from 0 to 31, and the recommended cofiguration is 7 or 15. |

REG_LED_INTERRUPT_CTRL_REG

Size : 32

Address offset : 020h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:5 |

RSVD |

R |

- |

Reserved |

4 |

GLOBAL_INT_EN |

R/W |

0 |

Global interrupt enable.

|

3 |

FIFO_OVERFLOW_INT_EN |

R/W |

0 |

FIFO overflow interrupt enable. When the data wriiten by software is more than internal FIFO level of LEDC, LEDC is in data loss state.

|

2 |

WAITDATA_TIMEOUT_INT_EN |

R/W |

0 |

The internal FIFO in LEDC can`t get data after the LED_WAIT_ DATA_TIME, the interrupt will be enable.

|

1 |

FIFO_CPUREQ_INT_EN |

R/W |

0 |

FIFO request CPU data interrupt enable.

|

0 |

LED_TRANS_FINISH_INT_EN |

R/W |

0 |

Data transmission complete interrupt enable.

|

REG_LED_INT_STS_REG

Size : 32

Address offset : 024h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:18 |

RSVD |

R |

- |

Reserved |

17 |

FIFO_EMPTY |

R |

0x1 |

FIFO empty status flag. When LEDC_EN is 0, FIFO_EMPTY equal 1. This flush residual d ata when LED_NUM is not integer multiples of burst length. |

16 |

FIFO_FULL |

R |

0 |

FIFO full status flag. |

15:4 |

RSVD |

R |

- |

Reserved |

3 |

FIFO_OVERFLOW_INT |

R/W |

0 |

FIFO overflow interrupt Clear 0 when software set LEDC_SOFT_RESET. The data written by external is more than the maximum storag e space of LEDC FIFO. At this time, software needs to deal w ith the abnormal situation.LEDC performs soft_reset operatio n to refresh all data.

|

2 |

WAITDATA_TIMEOUT_INT |

R/W |

0 |

Before transfer a frame: When the internal FIFO in LEDC can` t get data after the LED_WAIT_DATA_TIME,this bit is set. During transfer of a frame (between two pixel of data): To a void insert LED RESET between two pixel data, hardware will send WAITDATA_TIMEOUT_INT when wait_time>= min(RESET_TIME,LE D_WAIT_DATA_TIME). Clear 0 when software set LEDC_SOFT_RESET. When new data arrives at WAIT_DATA state, LEDC will continue sending data. Note : software should notice if the waiting time exceeds the operation of reset time, LEDC may enter refresh state, ne w data has not been sent.

|

1 |

FIFO_CPUREQ_INT |

R/W |

0 |

When FIFO data available is less than the threshold left, th e interrupt is reported to CPU. Clear 0 when software set LEDC_SOFT_RESET.

Note when get FIFO_CPUREQ_INT, CPU write 1 data to LEDC Buffer . It is inefficiently compares to DMA mode. |

0 |

LED_TRANS_FINISH_INT |

R/W |

0 |

When the data configured as TOTAL_DATA_LENGTH has been trans ferred complete, this bit is set. Clear 0 when software set LEDC_SOFT_RESET.

|

REG_LEDC_DEBUG_SEL_REG

Size : 32

Address offset : 030h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:9 |

RSVD |

R |

- |

Reserved |

8:7 |

LEDC_DEBUG_SEL_DRIVE |

R/W |

0 |

Drive module debug out select. |

6:3 |

LEDC_DEBUG_SEL_FIFO |

R/W |

0 |

Fifo module debug out select. [6:5] select debug_data of ledc_txfifo, valid range 0,1 [4:3] select output data byte when [6:5] is 0.

|

2:0 |

LEDC_DEBUG_SEL_TOP |

R/W |

0 |

Ledc top module debug out select. |