Audio

Audio IC Feature Support Table

Function |

RTL8721Dx |

RTL8720E |

RTL8726E |

RTL8713E |

RTL8730E |

RTL8721F |

|---|---|---|---|---|---|---|

I2S |

Y |

Y |

Y |

Y |

Y |

Y |

AMIC |

N |

N |

Y |

Y |

Y |

N |

DMIC |

Y |

Y |

Y |

Y |

Y |

Y |

VAD |

N |

N |

N |

N |

Y |

N |

PDM |

N |

Y |

Y |

Y |

Y |

N |

LINEOUT |

N |

N |

Y |

Y |

Y |

N |

HPO |

N |

N |

N |

N |

Y |

N |

Introduction

The audio whole block diagram is illustrated below.

Audio block consists of two parts:

SPORT: 2x

SPORT0 is for internal digital microphone interface and external I2S interface

SPORT1 is only for external I2S interface.

DMIC

Audio block consists of two parts:

SPORT: 2x

SPORT0 is for internal digital microphone interface and external I2S interface

SPORT1 is only for external I2S interface.

Audio codec:

DMIC: 4x

PDM: 1x

Audio block consists of two parts:

SPORT: 2x

SPORT0 is for internal digital microphone interface and external I2S interface

SPORT1 is only for external I2S interface.

Audio codec:

AMIC:3x

DMIC:4x

DAC: 1x

PDM: 1x

SPORT

SPORT Data Path

The data paths of SPORT 0/1/2/3 are shown below respectively.

SPORT0 data path

SPORT1 data path

SPORT2 data path

SPORT3 data path

Support SPORT0 and SPORT1.

Support SPORT0 and SPORT1.

Support SPORT0 and SPORT1.

Support SPORT0 and SPORT1.

Support SPORT0, SPORT1, SPORT2, SPORT3.

SPORT Function

SPORT Feature

General features

Supports up to 8-channel I2S transmitter

Supports 16/20/24/32 bits data length

Supports 16/20/24/32 bits channel length

Works in master and slave mode.

Supports sampling rate up to 192kHz

Support Multi-IO mode, fs up to 192kHz

General functions

SPORT fs counter and phase counter

SPORT fs counter and phase counter under BCLK

When using phase counter, rx_bclk_div_ratio/ tx_bclk_div_ratio should be configured to

63.Fs counter is used to count the number of LRCLK.

On every falling edge of LRCLK, phase counter would accumulate once in two BCLK cycles by default. On the next falling edge of LRCLK, phase counter will be reset to

0and then start counting again. At this time, the maximum accumulated value of phase counter is31.Phase counter also can accumulate once in one BCLK cycle, the maximum accumulated value of phase counter is

63.SPORT fs and phase counter is shown below:

SPORT fs counter and phase counter under SPORT CLK

SPORT CLK=98.304MHz/45.1584MHz. When the SPORT CLK is 98.304M, and on every rising edge or falling edge of LRCLK, the phase counter will accumulate once in one SPORT clock cycle, the accuracy of phase counter can reach 10ns.

Phase counter can start on the falling edge of LRCLK, and it increments by one at each SPORT CLK. On the next falling edge of LRCLK, phase counter will be reset to

0and then start to count again.Phase counter also can start on the rising edge of LRCLK, the rest is similar to the description above.

In master mode LRCLK is divided by SPORT CLK. In slave mode SPORT LRCLK is supported by master.

SPORT fs counter and phase counter under SPORT CLK is shown below:

Note

N = SPORT CLK/LRCLK

LRCLK start and stop detect: in slave mode, SPORT can use SPORT clock to monitor the start and stop of LRCLK.

Start condition: detect the rising edge or falling edge(default) of LRCLK. The implementation steps are as follows:

Stop condition: the phase counter is accumulated to a settable threshold. The implementation steps are as follows:

SPORT direct mode feature:

Used for data transmission between different sports without CPU and DMA involved in data transfer.

When two sports work in direct mode, clock needs to be at the same frequency.

SPORT FIFO:

TX_FIFO_0 and TX_FIFO_1 are two asynchronous ping-pong FIFO. Each FIFO is

depth=32andwidth=32, so2*32*4 bytes=64 words.RX_FIFO_0 and RX_FIFO_1 are two asynchronous ping-pong FIFO. Each FIFO is

depth=32andwidth=32, so2*32*4 bytes=64 words.6/8 channels for data transmission, FIFO0 and FIFO1 would be used. Two FIFOs will request at the same time, and four SPORTs will produce 16 requests at the same time.

WIFI TSF

WIFI TSF start SPORT

MAC sends interrupt to audio, and hardware will automatically start playing in audio side. The hardware delay is tens of nanoseconds. There is no need to wait for software to set MAC to send interrupt to open the following two bit functions.

((u32)SP0_CTRL0) &= ~ SP_BIT_TX_DISABLE; ((u32)SP0_CTRL0) |= SP_BIT_START_TX;

WIFI TSF latch SPORT counter

Hardware latch SPORT counter when it detects a change in the TSFT specified bit, software specifies the bits. The latch period is optional: 1.024/ 2.048/ 4.096 ……/ 131.072.

SPORT0 is for internal digital microphone interface and external I2S interface

SPORT1 is only for external I2S interface.

Not support LRCLK start and stop detect

Not support SPORT fs counter and phase counter under SPORT CLK

Support WIFI TSF,but not support WIFI TSF start SPORT

SPORT0 is for internal digital microphone interface and external I2S interface

SPORT1 is only for external I2S interface.

Not support LRCLK start and stop detect

Not support SPORT fs counter and phase counter under SPORT CLK

Not support WIFI TSF

SPORT0 is for internal digital microphone interface and external I2S interface

SPORT1 is only for external I2S interface.

Not support LRCLK start and stop detect

Not support SPORT fs counter and phase counter under SPORT CLK

Not support WIFI TSF

SPORT0 is for internal digital microphone interface and external I2S interface

SPORT1 is only for external I2S interface.

Not support LRCLK start and stop detect

Not support SPORT fs counter and phase counter under SPORT CLK

Not support WIFI TSF

SPORT0/1 is for internal audio codec and not support Multi-IO mode.

SPORT2/3 is for external I2S interface. In multi-I/O mode, fs supports up to 384kHz@master TX mode and slave RX mode, and other mode fs supports up to 192KHz.

Not support LRCLK start and stop detect

Not support SPORT fs counter and phase counter under SPORT CLK

Only

CHIP_DCUTsupports WIFI TSF, but not support WIFI TSF start SPORT

I2S Signal Introduction

The I2S bus has three lines:

Continuous serial clock (SCK/BCLK)

One SCK pulse generates a data bit

Master generates SCK

Word select (WS/LRCLK)

The word select line indicates the channel being transmitted:

WS = 0: channel 1 (left)WS = 1: channel 2 (right)

Changes one clock period before the MSB is transmitted

Serial data (SD)

SD is transmitted in two complements with the MSB first. The MSB has a fixed position, whereas the position of the LSB depends on the word length.

When the system word length is greater than the transmitter word length, the word is truncated (the least significant data bits are set to

0).If the receiver is sent more bits than its word length, the bits after the LSB are ignored.

If the receiver is sent fewer bits than its word length, the missing bits are set to zero internally.

I2S Data Format

The I2S interface supports I2S (Philips) format, Left-justified (MSB) format, Right-justified (LSB) format, PCM, and TDM mode. Software can select any mode by setting the I2S control register. The following figures show the I2S data format.

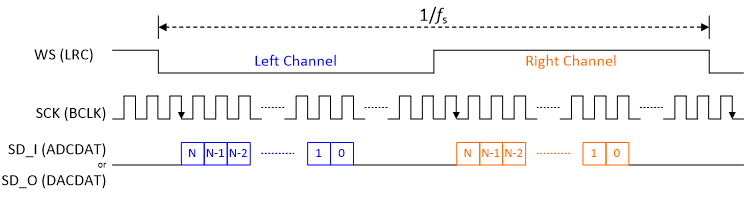

I2S format

Note

Typically, fs = 8/16/32/44.1/48/88.2/96/192/192kHz

Channel length: 16/20/24/32 bits (N+1)

SCK = Arbitrarily cycles within 1/fs, but

>= 2*(N+1) * fs, <= 256 * fs

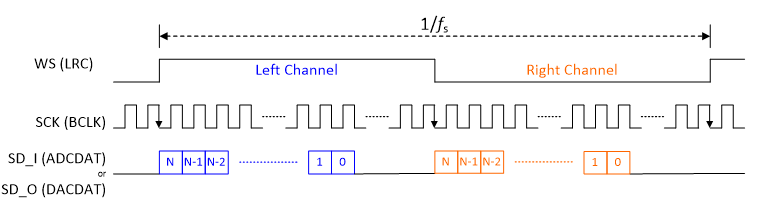

Left-justified format

Note

Typically, fs = 8/16/32/44.1/48/88.2/96/192/192kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 2*(N+1)*fs, <= 256 *fs

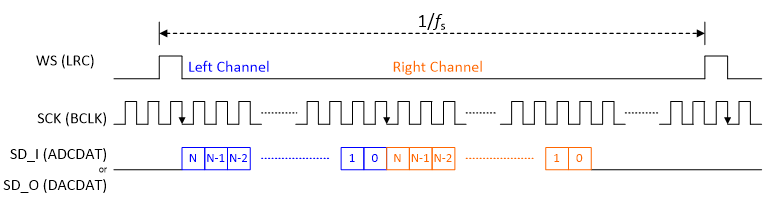

PCM mode A

Note

Typically, fs = 8/16/32/44.148/88.2/96/192kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 2*(N+1)*fs, <= 256 * fs

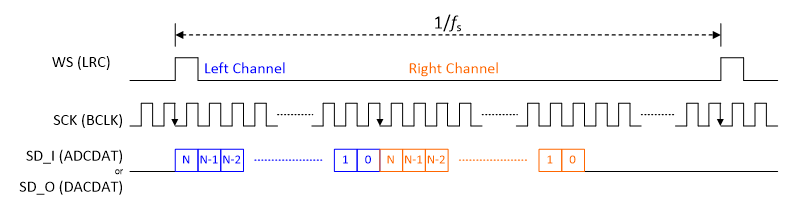

PCM mode B

Note

Typically, fs = 8/16/32/44.148/88.2/96/192kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 2*(N+1)*fs, <= 256 * fs

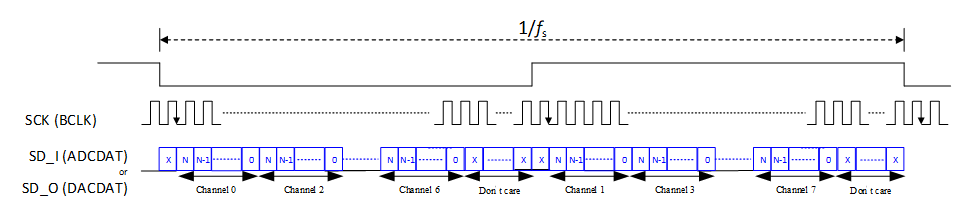

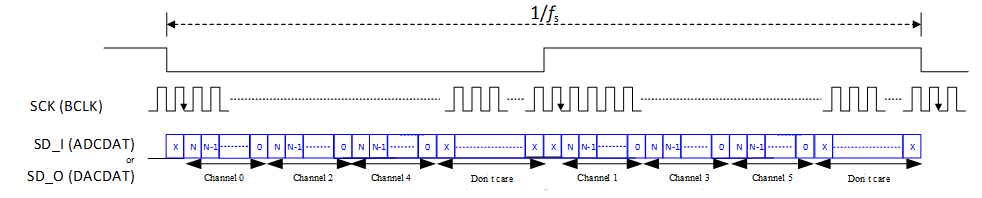

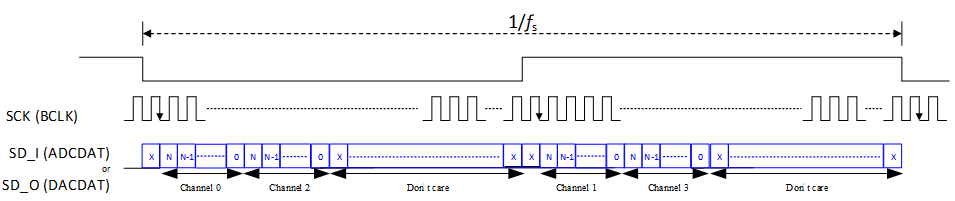

I2S TDM 8 mode

Note

Typically, fs = 8/16/32/44.1/48kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 8*(N+1)*fs, <= 256 * fs

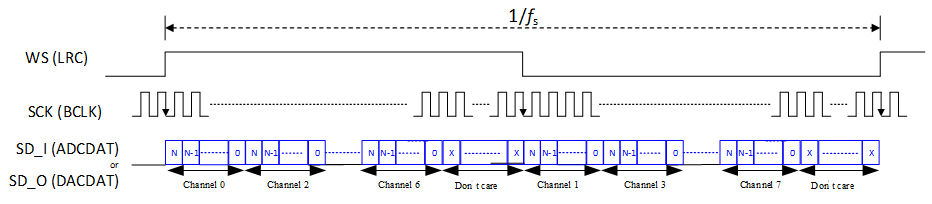

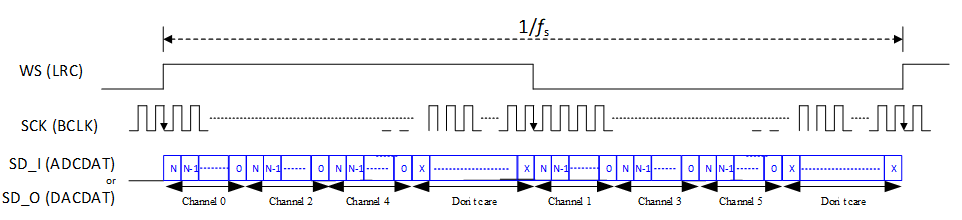

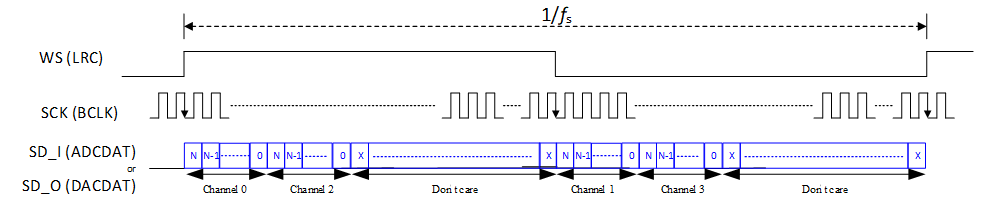

Left-justified TDM 8 mode

Note

Typically, fs = 8/16/32/44.1/48kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 8*(N+1)*fs, <= 256 * fs

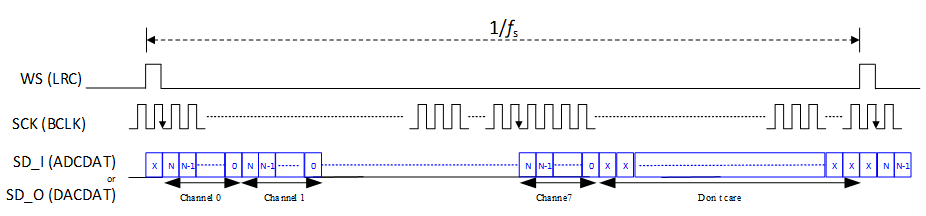

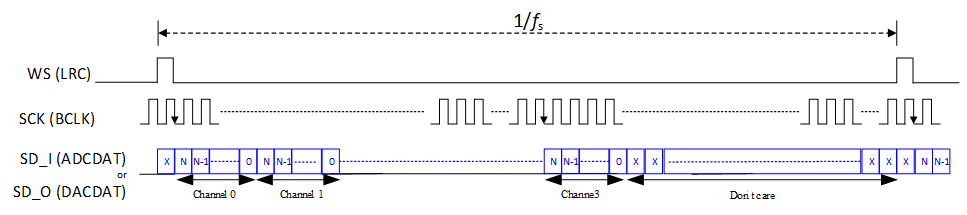

PCM mode A in TDM 8 mode

Note

Typically, fs = 8/16/32/44.1/48kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 8*(N+1)*fs, <= 256 * fs

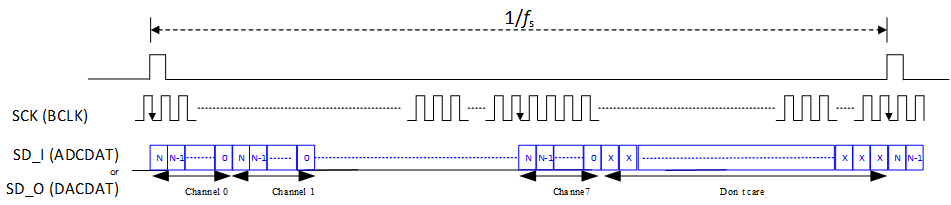

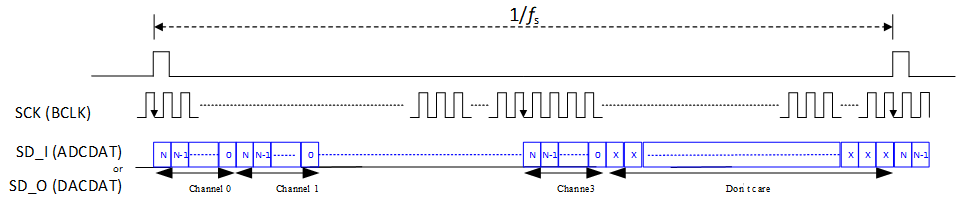

PCM mode B in TDM 8 mode

Note

Typically, fs = 8/16/32/44.1/48kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 8*(N+1)*fs, <= 256 *fs

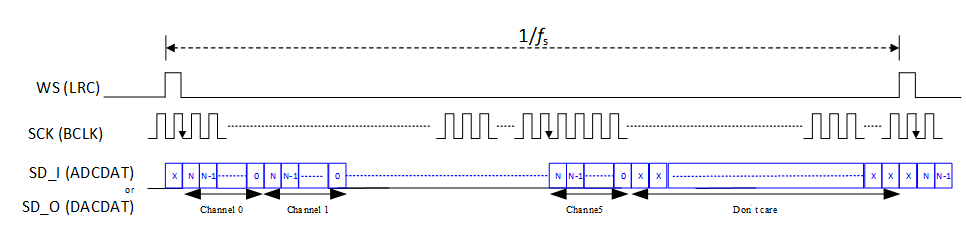

I2S TDM 6 mode

Note

Typically, fs = 8/16/32/44.1/48kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 6*(N+1)*fs, <= 256 * fs

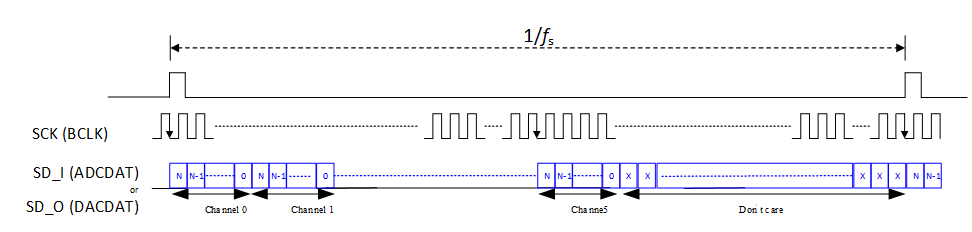

Left-justified TDM 6 mode

Note

Typically, fs = 8/16/32/44.1/48kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 6*(N+1)*fs, <= 256 * fs

PCM mode A in TDM 6 mode

Note

Typically, fs = 8/16/32/44.1/48kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 6*(N+1)*fs, <= 256 * fs

PCM mode B in TDM 6 mode

Note

Typically, fs = 8/16/32/44.1/48kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 6*(N+1)*fs, <= 256 * fs

I2S TDM 4 mode

Note

Typically, fs = 8/16/32/44.1/48/88.2/96kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 4*(N+1)*fs, <= 256 * fs

Left-justified TDM 4 mode

Note

Typically, fs = 8/16/32/44.1/48/88.2/96kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 4*(N+1)*fs, <= 256 * fs

PCM mode A in TDM 4 mode

Note

Typically, fs = 8/16/32/44.1/48/88.2/96kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 4*(N+1)*fs, <= 256 * fs

PCM mode B in TDM 4 mode

Note

Typically, fs = 8/16/32/44.1/48/88.2/96kHz

Channel length: 16/20/24/32 bits (N+1)

SCK >= 4*(N+1)*fs, <= 256 * fs

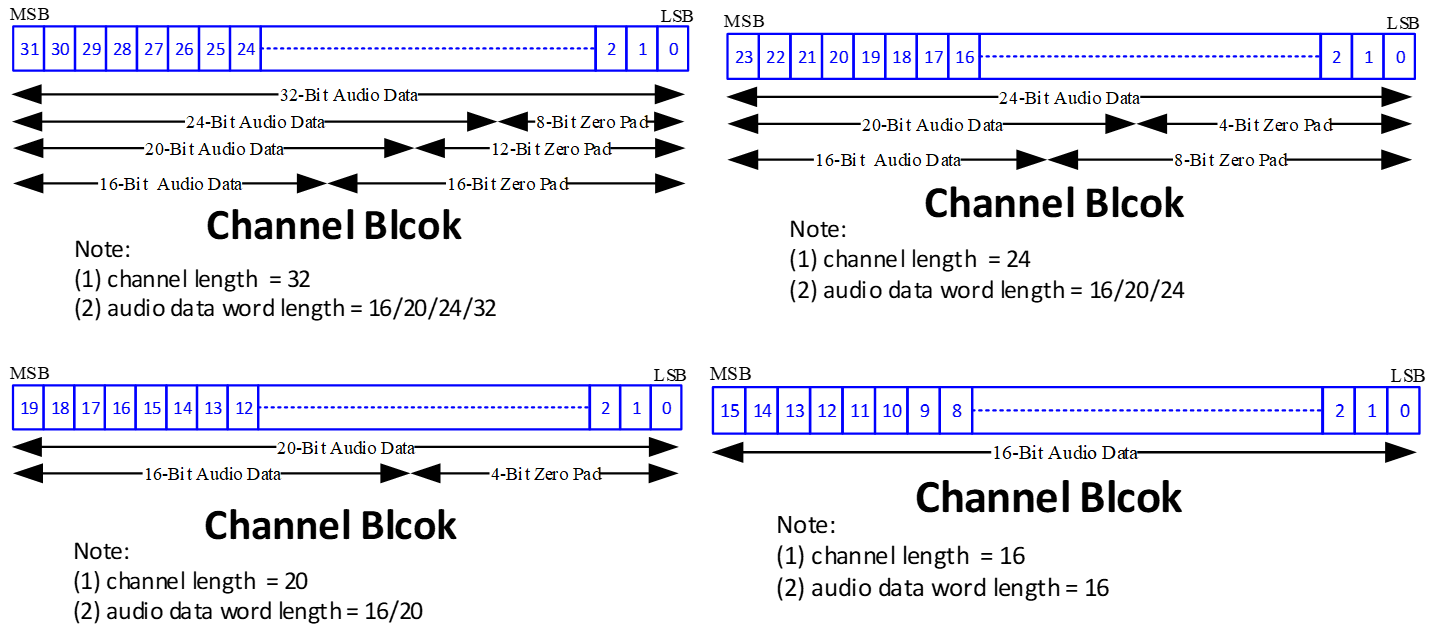

I2S supports 16/20/24/32 bits channel length, the relationship between audio data length and channel length is illustrated below.

SPORT Parameters

Interface/Format |

Sampling rate |

Audio bits |

Channel |

Channel length |

BCLK polarity |

Serial data |

Mode |

|---|---|---|---|---|---|---|---|

I2S |

192kHz |

16 bits |

Stereo |

16 bits |

BCLK |

MSB first |

Master |

Left-justified |

96kHz |

20 bits |

Mono |

20 bits |

BCLK inverse |

LSB first |

Slave |

PCM Mode A (Short Frame Sync) |

88.2kHz |

24 bits |

24 bits |

||||

PCM Mode A (Short Frame Sync) |

48kHz |

32 bits |

32 bits |

||||

PCM Mode B (Short Frame Sync) |

44.1kHz |

||||||

PCM Mode B (Short Frame Sync) |

32kHz |

||||||

16kHz |

|||||||

8kHz |

I2S PINMUX

The data PIN DIO[3:0] of I2S can be used as output or input. It can be set as input or output in the corresponding part of I2S in the PAD register. I2S data pinmux is shown below.

The data PIN DIO[3:0] of I2S can be used as output or input. It can be set as input or output in the corresponding part of I2S in the PAD register. I2S data pinmux is shown below.

The data PIN DIO[3:0] of I2S can be used as output or input. It can be set as input or output in the corresponding part of I2S in the PAD register. I2S data pinmux is shown below.

The data PIN DIO[3:0] of I2S can be used as output or input. It can be set as input or output in the corresponding part of I2S in the PAD register. I2S data pinmux is shown below.

The data PIN

DIN[3:0]of I2S is used as input.The data PIN

DOUT[3:0]of I2S is used as output.

Audio Codec

General Description

Audio codec provides 2-channel digital microphone for recording.

The audio codec is a high-performance, up to 4-channel I2S interface audio codec. The transmitted data can be from digital microphone input. Mono high-performance DAC are included.

Two smart digital mic interfaces are supported to make low jitter clock output and decimation filter for up to four digital mics. Independent digital voice controllers are provided in each channel.

PDM interface is supported for PDM digital speaker power amplifier.

An energy-based VAD module is built-in.

The audio codec is a high-performance, up to 4-channel I2S interface audio codec. The transmitted data can be from analog input or digital microphone input. The received data can stream to line output. Three channels analog ADCs and Mono high-performance DAC are included.

Audio codec integrates three ADCs with one mic bias voltage and mic boost amplifier to deliver valid channel data. The analog input port MICIN1_P/N ~ MICIN3_P/N is designed as full differential microphone pins or single-ended line-in pins. Two smart digital mic interfaces are supported to make low jitter clock output and decimation filter for up to four digital mics. Independent digital voice controllers are provided in each channel.

Audio codec integrates mono DAC with different output which actions as an input signal of headset or speaker power amplifier. And also a PDM interface is supported for PDM digital speaker power amplifier.

An energy-based VAD module is built-in.

The audio codec is a high-performance, up to 4-channel I2S interface audio codec. The transmitted data can be from analog input or digital microphone input. The received data can stream to line output. Three channels analog ADCs and Mono high-performance DAC are included.

Audio codec integrates three ADCs with one mic bias voltage and mic boost amplifier to deliver valid channel data. The analog input port MICIN1_P/N ~ MICIN3_P/N is designed as full differential microphone pins or single-ended line-in pins. Two smart digital mic interfaces are supported to make low jitter clock output and decimation filter for up to four digital mics. Independent digital voice controllers are provided in each channel.

Audio codec integrates mono DAC with different output which actions as an input signal of headset or speaker power amplifier. And also a PDM interface is supported for PDM digital speaker power amplifier.

An energy-based VAD module is built-in.

The audio codec is a high-performance, low-power, up to 8-channel I2S interface audio codec. The transmitted data can be from analog input or digital microphone input. The received data can stream to line output. Five channels analog ADCs can work in low power mode and normal mode. In low power and normal mode, THD+N of five channels ADCs all are about -80dB, and SNR can reach 98dBA. Two high-performance DACs are included, and THD+N of which are all about -85dB, and SNR can reach 98dBA.

Audio codec integrates five ADCs with independent mic bias voltage and mic boost amplifier to deliver valid channel data that channel crosstalk can be eliminated. The analog input port MIC0_P/N ~ MIC4_P/N is designed as full differential microphone pins or single-ended line-in pins. Four smart digital mic interfaces are supported to make low jitter clock output and decimation filter for up to eight digital mics. Independent digital voice controllers are provided in each channel.

Audio codec integrates two DACs with different output which actions as an input signal of headset or speaker power amplifier. And also a PDM interface is supported for PDM digital speaker power amplifier.

Audio codec includes several DSP features such as a high-pass filter, mixer, Equalizer, and volume control. The 10-band parametric Equalizer contains 10 independent filters with programmable gain, center frequency and bandwidth to tailor the frequency characteristics of the embedded playback system according to user preferences. The 5-band parametric Equalizer contains 5 independent filters with programmable gain, center frequency and bandwidth to tailor the frequency characteristics of the embedded record system according to user preferences.

Features

DMIC interface features:

8kHz/11.025kHz/12kHz/16kHz/22.5kHz/24kHz/32kHz/44.1kHz/48kHz/88.2kHz/96kHz for digital microphone interface

Asynchronous sample rate converter (ASRC) for each interface

Configurable 0-5 band EQ

Adjustable digital volume control

For digital volume control, supports zero-crossing detection to minimize audible artifacts

DC remove function

Audio codec features:

8k/11.025k/12k/16k/22.5k/24k/32k/44.1k/48k/88.2k/96kHz for PDM OUT

8k/11.025k/12k/16k/22.5k/24k/32k/44.1k/48k/88.2k/96kHz forDMIC interface

Asynchronous sample rate converter (ASRC) for each interface

For digital volume control, supports zero-crossing detection to minimize audible artifacts

DC remove function for DMIC and PDM.

PDM interface function for external speaker AMP

Audio codec features:

Analog features

DAC with 98dB A-weighted SNR

ADC with 98dB A-weighted SNR

Differential analog microphone inputs with boost pre-amplifiers and low noise microphone bias

0/5/10/15/20/25/30/35/40dB microphone boost gain

MIC input to ADC with 0dB boost gain in low power mode,

SNR > 98dBA-weighted and THD+N is about -80 dB-80dB crosstalk between channels

Adjustable MICBIAS with less than -100dBV noise floor and -70dB PSRR

Mono DAC output with lineout

SNR >= 98dBA-weighted (AVDD=1.8V, load=10kΩ, differential output, 25℃)THD+N is about -85 dB (

AVDD=1.8V, load=10kΩ, differential output, 25℃)Differential output

-80dB crosstalk between channels

Digital features

8k/11.025k/12k/16k/22.5k/24k/32k/44.1k/48k/88.2k/96k/176.4k/192kHz for DAC path

8k/11.025k/12k/16k/22.5k/24k/32k/44.1k/48k/88.2k/96kHz for ADC path

Digital microphone interface supported

Asynchronous sample rate converter (ASRC) for each interface

For digital volume control, supports zero-crossing detection to minimize audible artifacts

DC remove function for ADC, DAC

PDM interface function for external speaker AMP

Audio codec features:

Analog features

DAC with 98dB A-weighted SNR

ADC with 98dB A-weighted SNR

Differential analog microphone inputs with boost pre-amplifiers and low noise microphone bias

0/5/10/15/20/25/30/35/40dB microphone boost gain

MIC input to ADC with 0dB boost gain in low power mode,

SNR > 98dBA-weighted and THD+N is about -80 dB-80dB crosstalk between channels

Adjustable MICBIAS with less than -100dBV noise floor and -70dB PSRR

Mono DAC output with lineout

SNR >= 98dBA-weighted (AVDD=1.8V, load=10kΩ, differential output, 25℃)THD+N is about -85 dB (

AVDD=1.8V, load=10kΩ, differential output, 25℃)Differential output

-80dB crosstalk between channels

Digital features

8k/11.025k/12k/16k/22.5k/24k/32k/44.1k/48k/88.2k/96k/176.4k/192kHz for DAC path

8k/11.025k/12k/16k/22.5k/24k/32k/44.1k/48k/88.2k/96kHz for ADC path

Digital microphone interface supported

Asynchronous sample rate converter (ASRC) for each interface

For digital volume control, supports zero-crossing detection to minimize audible artifacts

DC remove function for ADC, DAC

PDM interface function for external speaker AMP

Audio codec features:

Analog features

DAC with 98dBA SNR

ADC with 98dBA SNR

Differential analog microphone inputs with boost pre-amplifiers and low noise microphone bias

0/5/10/15/20/25/30/35/40dB microphone boost gain

MIC input to ADC with 0dB boost gain in normal mode,

SNR > 98dBAandTHD+N is about -80dBMIC input to ADC with 0dB boost gain in low power mode,

SNR > 90dBAandTHD+N is about -78dB-80dB crosstalk between channels

Adjustable MICBIAS with less than -100dBV noise floor and -70dB PSRR

Dual Stereo DAC outputs with stereo headphone amplifiers

SNR >= 98dBA(AVDD=1.8V,load=10kΩ, dual differential output)THD+N is about -85dB (

AVDD=1.8V,load=10kΩ, dual differential output)Dual differential output

-80dB crosstalk between channels

De-pop function in stereo headphone amplifiers

Digital features

8k/11.025k/12k/16k/22.5k/24k/32k/44.1k/48k/88.2k/96k/176.4k/192kHz for DAC path

8k/11.025k/12k/16k/22.5k/24k/32k/44.1k/48k/88.2k/96kHz for ADC path

Digital microphone interface supported

Asynchronous sample rate converter (ASRC) for each interface

10-bands flexible equalizer (EQ) for DAC path

Configurable 0-5 band EQ in 6 channels for ADC path

Adjustable digital volume control in ADC, DAC

For digital volume control, supports zero-crossing detection to minimize audible artifacts

DC remove function for ADC, DAC

PDM interface function for external speaker AMP

Side tone function

Audio Codec Data Path

Recording Data Path

The following figure shows the recording data path of digital microphone interface. In the recording path, the input source is 2-channel DMIC.

The following figure shows the recording data path of audio codec. In the recording path, the input source can be selected DMIC 0-3, and MUSIC_OUT.

DMIC 0-3 is the data from 4 channel digital microphones.

MUSIC_OUT is the data from DAC SDM out for AEC reference signal.

The following figure shows the recording data path of audio codec. In the recording path, the input source can be selected from ADC 1-3, DMIC 0-3, and MUSIC_OUT.

ADC 1-3 is the data from 3 channel analog ADC

DMIC 0-3 is the data from 4 channel digital microphones.

MUSIC_OUT is the data from DAC SDM out for AEC reference signal.

The following figure shows the recording data path of audio codec. In the recording path, the input source can be selected from ADC 1-3, DMIC 0-3, and MUSIC_OUT.

ADC 1-3 is the data from 3 channel analog ADC

DMIC 0-3 is the data from 4 channel digital microphones.

MUSIC_OUT is the data from DAC SDM out for AEC reference signal.

The following figure shows the recording data path of audio codec. In the recording path, the input source can be selected from ADC 0-4, DMIC 0-7, and MUSIC_OUT.

ADC 0-4 is the data from 5 channel analog ADC

DMIC 0-7 is the data from 8 channel digital microphones.

MUSIC_OUT is the data from DAC SDM out.

Playback Data Path

Not support.

The following figure shows the playback data path of audio codec, which can be SP_L and reference signal.

SP_L is the data from music channel left.

Reference signal is the data from reference signal module for test.

The following figure shows the playback data path of audio codec, which can be SP_L and reference signal.

SP_L is the data from music channel left.

Reference signal is the data from reference signal module for test.

The following figure shows the playback data path of audio codec, which can be SP_L and reference signal.

SP_L is the data from music channel left.

Reference signal is the data from reference signal module for test.

The following figure shows the playback data path of audio codec, which can be SP_L, SP_R, SP_L + SP_R, and reference signal.

SP_Lis the data from music channel left.SP_Ris the data from music channel right.SP_L + SP_Ris the data from music channel left added channel right.Reference signalis the data from reference signal module for test.

Audio Codec Functional Description

Audio codec provides 2-channel digital microphone for recording.

Audio codec provides 1-channel digital interface for PDM.

Audio codec provides 1-channel analog DAC for playback and 3-channel analog ADCs for recording.

Audio codec provides 1-channel analog DAC for playback and 3-channel analog ADCs for recording.

Audio codec provides 2-channel analog DACs for playback and 5-channel analog ADCs for recording.

Audio Recording

Audio Recording Block

The digital microphone (DMIC) interface is for digital microphone, and supports 2-channel digital microphone recording. The following figure shows the details block of digital microphone interface.

There are three analog ADCs and with up to 3-channel recording paths. You can use three microphones to pass to analog ADCs. Three-channel ADCs has two type analog input ports: microphone input and line input, which all support differential and single end.

The IN1-3P/N are microphone-type input ports. The input port can be configured to differential input or single-ended input. The microphone input port has its microphone bias and microphone boost. The low noise microphone bias can improve recording performance and enhance recording quality. Built-in short current detection scheme can be used for switch detection. Multi-step microphone boost gain is easy to use for microphone applications. The following figure shows the recording analog block.

A boost amplifier is provided in the input path to the ADC, which can be used manually with 5dB step from 0dB to 40dB, to keep the recording volume constant.

Analog and digital MIC recording path

The recording part includes one programmable microphone bias output, capable of providing output voltages of 1.8V with 3mA output-current drive capability. It can be powered down completely when not needed for power saving. The following figure shows the function block of MICBIAS.

There are three analog ADCs and with up to 3-channel recording paths. You can use three microphones to pass to analog ADCs. Three-channel ADCs has two type analog input ports: microphone input and line input, which all support differential and single end.

The IN1-3P/N are microphone-type input ports. The input port can be configured to differential input or single-ended input. The microphone input port has its microphone bias and microphone boost. The low noise microphone bias can improve recording performance and enhance recording quality. Built-in short current detection scheme can be used for switch detection. Multi-step microphone boost gain is easy to use for microphone applications. The following figure shows the recording analog block.

A boost amplifier is provided in the input path to the ADC, which can be used manually with 5dB step from 0dB to 40dB, to keep the recording volume constant.

Analog and digital MIC recording path

The recording part includes one programmable microphone bias output, capable of providing output voltages of 1.8V with 3mA output-current drive capability. It can be powered down completely when not needed for power saving. The following figure shows the function block of MICBIAS.

There are five analog ADCs and with up to 5-channel recording paths. You can use five microphones to pass to analog ADCs. Five channel ADCs has two type analog input ports: microphone input and line input, which all support differential and single-ended.

The IN0-4P/N are microphone-type input ports. The input port can be configured to differential input or single-ended input. The microphone input port has its microphone bias and microphone boost. The low noise microphone bias can improve recording performance and enhance recording quality. Build-in short current detection scheme can be used for switch detection. Multi-step microphone boost gain is easy to use for microphone applications. The following figure shows the recording analog block.

A boost amplifier is provided in the input path to the ADC, which can be used manually with 5dB step from 0dB to 40dB, to keep the recording volume constant.

There are up to 8-channel digital microphone interface which shares the digital path with AMIC ADC.

Analog and digital MIC recording path

The recording part includes five programmable microphone bias outputs (MICBIAS0, MICBIAS1, MICBIAS2, MICBIAS3, MICBIAS4), capable of providing output voltages of 1.8V with 3mA output-current drive capability. In addition, the MICBIAS outputs may be programmed to be switched to AVCC_DRV directly through an on-chip switch, and it can be powered down completely when no need for power saving. The following figure shows the function block of MICBIAS.

Note

In low power mode, the power supply of external AMIC should be switched to AVCC_DRV. You can configure GPIO<16:12> to output HIGH to realize it. This is equivalent to that the phase inverter outputs high level, and software conduction resistance is about 33Ω.

Digital Feature of Audio Recording

Recording path for sampling rate 8k/11.025k/12k/16k/32k/22.05k/44.1k/48k/88.2k/96kHz

ASRC (asynchronous sample rate converter)

The ADC digital part supports digital volume control, and the gain is between 48dB and -17.625dB in 0.375dB per step.

There is a high pass filter for DC offset

Zero-crossing function

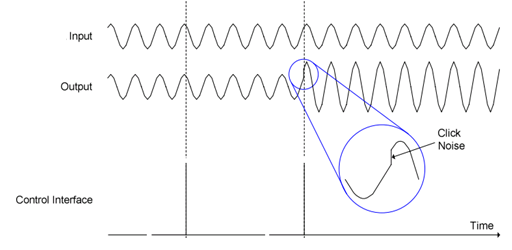

If the volume is adjusted while the signal is a non-zero value, an audible click can occur, as shown below.

Click noise without zero crossing

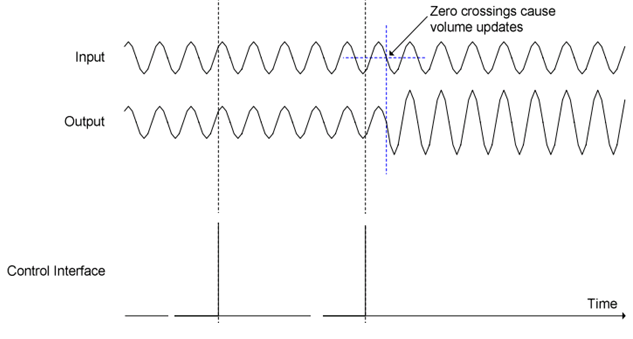

In order to prevent this click noise, a zero-crossing function is provided. When enabled, this will cause the volume to update only when a zero crossing occurs, minimizing click noise, as shown below.

Minimizing click noise with zero crossing

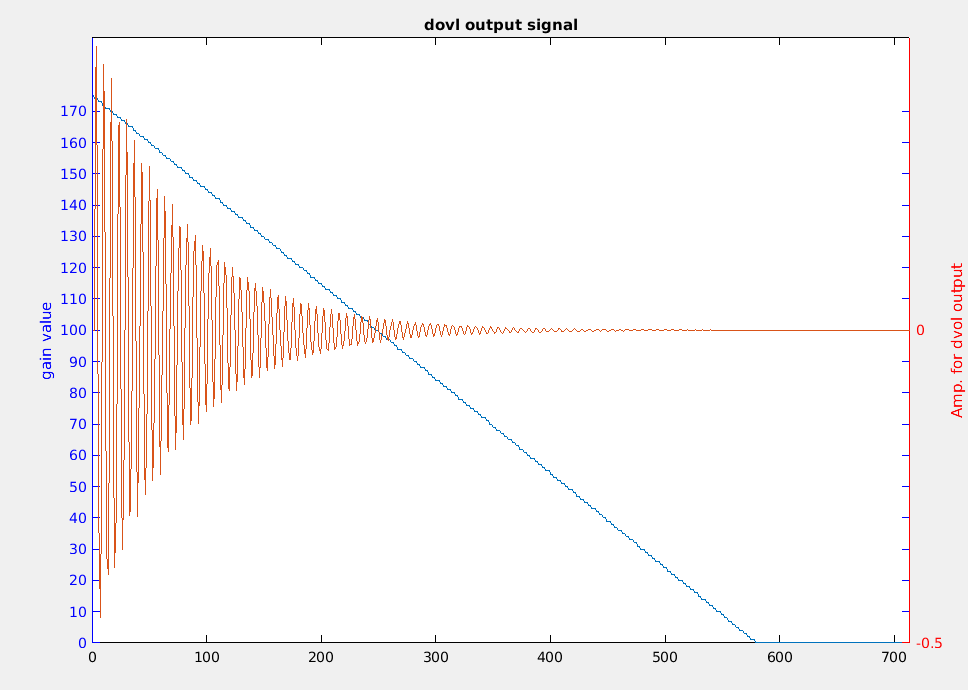

When the signal is very quiet and consists of mainly of noise, zero crossing cannot be met, now the gain will change with steps, as shown below.

Gain update with steps as zero crossing

Equalizer block

The equalizer block cascades 0-5 bands of equalizer to tailor the frequency characteristics of the recording system according to user preferences and to emulate environment sound.

DC remove function block

A high pass filter is implemented for dc offset. The high pass filter is mainly for ADC recording used. The cut-off frequency of filter is programmable and is varied according to different sample rates. The filter is used to remove DC offset at normal conditions.

Silence detector block

The Silence detector is used to reduce the noise floor for DAC path or ADC path. When the input signal is below silence level, the input signal will be reduced to suppress the background noise. The reducing level can be set by registers.

Not support equalizer block.

Not support equalizer block.

Not support equalizer block.

Audio Playback

Not support.

Build-in 1-channel PDM out interface, connected to a PDM speaker amplifier to playback.

Build-in 1-channel sigma-delta DAC is an on-chip Sigma-Delta Modulator, and a 24-bit input high-performance current steering DAC is composed of it. The analog part controls the current cell by the signal from digital part, and changes digital signal to analog signal and sends to Power Amplifier (PA).

Build-in 1-channel sigma-delta DAC is an on-chip Sigma-Delta Modulator, and a 24-bit input high-performance current steering DAC is composed of it. The analog part controls the current cell by the signal from digital part, and changes digital signal to analog signal and sends to Power Amplifier (PA).

Build-in 2-channel sigma-delta DAC is an on-chip Sigma-Delta Modulator, and a 24-bit input high-performance current steering DAC is composed of it. The analog part controls the current cell by the signal from digital part, and changes digital signal to analog signal and sents to Power Amplifier (PA).

Audio Playback Block

Not support.

Built-in high-performance stereo current steering DAC, and with stereo headphone driver amplifiers, the amplifiers support differential output and an anti-pop circuit can suppress the noise of amplifier when power up effectively. The headphone driver amplifiers include 4 level volume control, which decreases 3dB by one step. LOUT signal is from DAC_L.

Built-in a PDM interface, for PDM speaker amplifier, the interface will support mono speaker.

Built-in high-performance stereo current steering DAC, and with stereo headphone driver amplifiers, the amplifiers support differential output and an anti-pop circuit can suppress the noise of amplifier when power up effectively. The headphone driver amplifiers include 4 level volume control, which decreases 3dB by one step. LOUT signal is from DAC_L.

Built-in a PDM interface, for PDM speaker amplifier, the interface will support mono speaker.

Built-in high-performance stereo current steering DAC, and with stereo headphone driver amplifiers, the amplifiers support differential output and an anti-pop circuit can suppress the noise of amplifier when power up effectively. The headphone driver amplifiers include 4 level volume control, which decreases 3dB by one step. LOUT signal is from DAC_L and ROUT signal is from DAC_R.

Analog of audio playback block

Built-in a PDM interface, for PDM speaker amplifier, the interface will support stereo speaker.

Digital Feature of Audio Playback

Not support.

Playback path for sample rate 8K,11.025K,12K,16K,32K,22.05K,44.1K 48kHz,88.2K,96kHz, 176.4K,192K

ASRC supports up to 96kHZ sample rate

The DAC digital part support digital volume control, and the gain is between 0dB and -65.625dB in 0.375dB/step.

There is a high pass filter for DC offset, the cut-off frequency of filter is programmable and is varied according to different sample rates.

Zero crossing function, this function is the same as ADC zero crossing.

Silence detector block

The Silence detector is used to reduce the noise floor for DAC path or ADC path. When the input signal is below silence level, the input signal will be reduced to suppress the background noise. The reducing level can be set by registers.

PDM interface

Test tone

Built-in a test tone module, the tone frequency can be configured by

(fs/192)*(tone_fc_sel+1)kHz, and the tone gain can be configured by0 ~ 6.02*(gain_sel)dB.

Playback path for sample rate 8K,11.025K,12K,16K,32K,22.05K,44.1K 48kHz,88.2K,96kHz, 176.4K,192K

ASRC supports up to 96kHZ sample rate

The DAC digital part support digital volume control, and the gain is between 0dB and -65.625dB in 0.375dB/step.

There is a high pass filter for DC offset, the cut-off frequency of filter is programmable and is varied according to different sample rates.

Zero crossing function, this function is the same as ADC zero crossing.

Silence detector block

The Silence detector is used to reduce the noise floor for DAC path or ADC path. When the input signal is below silence level, the input signal will be reduced to suppress the background noise. The reducing level can be set by registers.

PDM interface

Test tone

Built-in a test tone module, the tone frequency can be configured by

(fs/192)*(tone_fc_sel+1)kHz, and the tone gain can be configured by0 ~ 6.02*(gain_sel)dB.

Playback path for sample rate 8K,11.025K,12K,16K,32K,22.05K,44.1K 48kHz,88.2K,96kHz, 176.4K,192K

ASRC supports up to 96kHZ sample rate

The DAC digital part support digital volume control, and the gain is between 0dB and -65.625dB in 0.375dB/step.

There is a high pass filter for DC offset, the cut-off frequency of filter is programmable and is varied according to different sample rates.

Zero crossing function, this function is the same as ADC zero crossing.

Silence detector block

The Silence detector is used to reduce the noise floor for DAC path or ADC path. When the input signal is below silence level, the input signal will be reduced to suppress the background noise. The reducing level can be set by registers.

PDM interface

Test tone

Built-in a test tone module, the tone frequency can be configured by

(fs/192)*(tone_fc_sel+1)kHz, and the tone gain can be configured by0 ~ 6.02*(gain_sel)dB.

Playback path for sample rate 8K,11.025K,12K,16K,32K,22.05K,44.1K 48kHz,88.2K,96kHz, 176.4K,192K

Asynchronous Sample Rate Converters (ASRC)

The DAC digital part support digital volume control, and the gain is between 0dB and -65.625dB in 0.375dB per step.

There is a high pass filter for DC offset, the cut-off frequency of filter is programmable and is varied according to different sample rates.

Zero-crossing function, which is the same as ADC zero-crossing.

PDM interface

Test tone

Built-in a test tone module, the tone frequency can be configured by

(fs/192) * (tone_fc_sel+1) kHz, and the tone gain can be configured by0 ~ 6.02 * (gain_sel) dBChannel L and channel R mix

Before streaming to DAC, channel L data and channel R data are mixed, then streamed to DAC_L channel and DAC_R channel.

VAD_PITCH

VAD_PITCH Features

VAD (Voice Activity Detection) is a low-energy voice detect IP. It supports voice trigger. Once the VAD function is enabled, it will automatically sample the voice and detect the voice energy above the threshold value or not, even the processor is in sleep mode.

The overall design of VAD mainly includes two aspects, one is the generation of wake-up interrupt, to wake up the processor; the other is the transmission of voice data after wake-up, to let the processor timely access to audio data for keyword recognition.

VAD data source may be up to four analog microphones, and up to eight digital microphones. The VAD can configure software to choose which audio source to use as input. An APB configuration interface is also supported. When the VAD successfully recognizes a human voice in CPU low power mode, an interrupt is generated and reported to the CPU.

SRAM is used to store audio data buffer during power consumption. It is 128KB in size and supports 64 bits read/write. The data source is parallel to the VAD’s audio data source and is also audio data after the MUX.

At the same time, SRAM can also be read and written by KM0, KM4 and CA32 at workflow.

Not support VAD_PITCH

Not support VAD_PITCH

Not support VAD_PITCH

Not support VAD_PITCH

Support VAD_PITCH

Register

SPORT Register

Base Address:

SPORT0_REG : 0x4012A000

SPORT1_REG : 0x4012B000

Name |

Address offset |

Access |

Description |

|---|---|---|---|

000h |

R/W |

||

004h |

R/W |

||

008h |

R/W |

||

00Ch |

R/W |

||

014h |

R |

||

018h |

R |

||

01Ch |

R/W |

||

020h |

R/W |

||

024h |

R |

||

028h |

R/W |

||

02Ch |

R/W |

||

030h |

R/W |

||

034h |

R |

||

03Ch |

R/W |

||

044h |

R/W |

||

048h |

R/W |

||

04Ch |

R/W |

||

054h |

R/W |

||

058h |

R/W |

||

05Ch |

R/W |

||

060h |

R |

||

064h |

R/W |

||

800h |

R/W |

||

880h |

R |

||

900h |

R/W |

||

980h |

R |

REG_SP_REG_MUX

Name : SPORT MUX Register

Size : 32

Address offset : 000h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

SP_REG_MUX |

R/W |

0xFFFFFFFF |

Mux of register write with different base address of the sam e SPORT. This field can be set as different value with four different base address in one SPORT, but other registers share the sam e value with four different base address in one SPORT. |

REG_SP_CTRL0

Name : SPORT Control Register 0

Size : 32

Address offset : 004h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:30 |

MCLK_SEL |

R/W |

0x0 |

Not used, refer to 0x64 2’b00: MCLK output=dsp_src_clk/4 2’b01: MCLK output=dsp_src_clk/2 2’b10/2’b11: MCLK output=dsp_src_clk |

29:28 |

SP_SEL_I2S_RX_CH |

R/W |

0x0 |

2’b00: L/R 2’b01: R/L 2’b10: L/L 2’b11: R/R x ADC path |

27:26 |

SP_SEL_I2S_TX_CH |

R/W |

0x0 |

2’b00: L/R 2’b01: R/L 2’b10: L/L 2’b11: R/R x DAC path |

25 |

SP_START_RX |

R/W |

0 |

1’b0: Rx is disabled 1’b1: Rx is started |

24 |

SP_RX_DISABLE |

R/W |

1 |

1’b1: SPORT Rx is disabled. 1’b0: SPORT Rx is enabled. |

23 |

RX_LSB_FIRST_0 |

R/W |

0 |

1’b0: MSB first when Rx 1’b1: LSB first |

22 |

TX_LSB_FIRST_0 |

R/W |

0 |

1’b0: MSB first when Tx 1’b1: LSB first |

21:20 |

SP_TDM_MODE_SEL_RX |

R/W |

0x0 |

2’b00: Without TDM 2’b01: TDM4 2’b10: TDM6 2’b11: TDM8 |

19:18 |

SP_TDM_MODE_SEL_TX |

R/W |

0x0 |

2’b00: Without TDM 2’b01: TDM4 2’b10: TDM6 2’b11: TDM8 |

17 |

SP_START_TX |

R/W |

0 |

1’b0: Tx is disabled. 1’b1: Tx is started. |

16 |

SP_TX_DISABLE |

R/W |

1 |

1’b1: SPORT Tx is disabled. 1’b0: SPORT Tx is enabled. |

15 |

SP_I2S_SELF_LPBK_EN |

R/W |

0 |

1’b1: internal loopback mode is enabled |

14:12 |

SP_DATA_LEN_SEL_TX_0 |

R/W |

0x0 |

3’b000: 16 bits 3’b001: 20 bits 3’b010: 24 bits 3’b100: 32 bits |

11 |

SP_EN_I2S_MONO_TX_0 |

R/W |

0 |

1’b1: mono 1’b0: stereo |

10 |

SP_INV_I2S_SCLK |

R/W |

0 |

1’b1: I2S/PCM bit clock is inverted |

9:8 |

SP_DATA_FORMAT_SEL_TX |

R/W |

0x0 |

2’b00: I2S 2’b01: Left-justified 2’b10: PCM mode A 2’b11: PCM mode B |

7 |

DSP_CTL_MODE |

R/W |

0 |

1’b1: DSP and SPORT1 handshaking is enabled. 1’b0: GDMA and SPORT1 handshaking is enabled. |

6 |

SP_LOOPBACK |

R/W |

0 |

1’b1: self-loopback mode |

5 |

SP_WCLK_TX_INVERSE |

R/W |

0 |

1’b1: I2S/PCM word clock is inverted for Tx (SPK path) |

4 |

SLAVE_DATA_SEL |

R/W |

0 |

1’b1: To be an I2S or PCM slave (data path) |

3 |

SLAVE_CLK_SEL |

R/W |

0 |

1’b1: To be an I2S or PCM slave (CLK path) |

2 |

RX_INV_I2S_SCLK |

R/W |

0 |

|

1 |

TX_INV_I2S_SCLK |

R/W |

0 |

|

0 |

SP_RESET |

R/W |

0 |

1’b1: reset SPORT1 module, and remember to write “1” to rese t and then write “0” to release from reset. |

REG_SP_CTRL1

Name : SPORT Control Register 1

Size : 32

Address offset : 008h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

RX_FIFO_1_REG_1_EN |

R/W |

0 |

1’b1: Enable last two channels of RX_FIFO_1. Only enable whe n RX_FIFO_1_REG_1_EN = 1. |

30 |

RX_FIFO_1_REG_0_EN |

R/W |

0 |

1’b1: Enable first two channels of RX_FIFO_1. Only enable wh en RX_FIFO_0_REG_0_EN = 1. |

29 |

RX_FIFO_0_REG_1_EN |

R/W |

0 |

1’b1: Enable last two channels of RX_FIFO_0. Only enable whe n RX_FIFO_0_REG_0_EN = 1. |

28 |

RX_FIFO_0_REG_0_EN |

R/W |

1 |

1’b1: Enable first two channels of RX_FIFO_0. Disable 0x0008 [28] ~ Disable 0x0008[31] at the same time to reset Rx FIFO. |

27 |

TX_FIFO_1_REG_1_EN |

R/W |

0 |

1’b1: Enable last two channels of TX_FIFO_1. Only enable whe n TX_FIFO_1_REG_0_EN = 1. |

26 |

TX_FIFO_1_REG_0_EN |

R/W |

0 |

1’b1: Enable first two channels of TX_FIFO_1. Only enable wh en TX_FIFO_0_REG_0_EN = 1. |

25 |

TX_FIFO_0_REG_1_EN |

R/W |

0 |

1’b1: Enable last two channels of TX_FIFO_0. Only enable whe n TX_FIFO_0_REG_0_EN = 1. |

24 |

TX_FIFO_0_REG_0_EN |

R/W |

1 |

1’b1: Enable first two channels of TX_FIFO_0. Disable 0x0008 [24] ~ Disable 0x0008[27] at the same time to reset Tx FIFO. |

23 |

RX_SNK_LR_SWAP_0 |

R/W |

0 |

1’b1: swap L/R audio samples written to the sink memory of R X_FIFO_0 |

22 |

RX_SNK_BYTE_SWAP_0 |

R/W |

0 |

1’b1: swap H/L bytes written to the sink memory of RX_FIFO_0 |

21 |

TX_SRC_LR_SWAP_0 |

R/W |

0 |

1’b1: swap L/R audio samples read from the source memory of TX_FIFO_0 |

20 |

TX_SRC_BYTE_SWAP_0 |

R/W |

0 |

1’b1: swap H/L bytes read from the source memory of TX_FIFO_ 0 |

19 |

DIRECT_MODE_EN |

R/W |

0 |

1’b1: WS (LRCK) and SCK (BCLK) are from other SPORT |

18:17 |

SP_DIRECT_SRC_SEL |

R/W |

0x0 |

2’b00: WS and SCK are from SPORT0. 2’b01: WS and SCK are from SPORT1. 2’b10: WS and SCK are from SPORT2. 2’b11: WS and SCK are from SPORT3. |

16 |

ERR_CNT_SAT_SET |

R/W |

0 |

1’b1: saturation count (65534 -> 65535 -> 65535 …) 1’b0: wrap count (65534 -> 65535 -> 0 -> 1 -> 2 …) |

15:14 |

SPORT_CLK_SEL |

R/W |

0x0 |

2’b0x00: dsp_src_clk (BCLK*2) 2’b10: dsp_src_clk (BCLK*4)/2 2’b11: dsp_src_clk (BCLK*8)/4 |

13 |

CLEAR_RX_ERR_CNT |

R/W |

0 |

Write 1’b1 and then write 0 to clear Rx error counter |

12 |

CLEAR_TX_ERR_CNT |

R/W |

0 |

Write 1’b1 and then write 0 to clear Tx error counter |

11 |

ENABLE_MCLK |

R/W |

0 |

Enable mclk. |

10:8 |

DEBUG_BUS_SEL |

R/W |

0x0 |

3’b000: debug_bus_a 3’b001: debug_bus_b … 3’b111: debug_bus_h |

7 |

WS_FORCE_VAL |

R/W |

1 |

When WS_FORCE = 1, ws_out_tx and ws_out_rx = “ws_force_val” |

6 |

WS_FORCE |

R/W |

0 |

|

5 |

BCLK_RESET |

R/W |

0 |

1’b0: Enable bclk 1’b1: Disable and reset bclk |

4 |

BCLK_PULL_ZERO |

R/W |

0 |

Write 1’b1 to pull bclk to 0 smoothly Write 1’b0 to reopen bclk |

3 |

MULTI_IO_EN_RX |

R/W |

1 |

1’b1: Enable multi-IO of Rx 1’b0: Disable multi-IO of Rx |

2 |

MULTI_IO_EN_TX |

R/W |

1 |

1’b1: Enable multi-IO of Tx 1’b0: Disable multi-IO of Tx |

1 |

TX_FIFO_FILL_ZERO |

R/W |

0 |

X is the burst size of TX_FIFO_0. Y is the burst size of TX_ FIFO_1. Fill TX_FIFO_0 with X zero data and fill TX_FIFO_1 with Y ze ro data. This control bit is “write 1 clear” type |

0 |

SP_RESET_SMOOTH |

R/W |

0 |

1’b1: reset SPORT1 module with complete LRCK cycle. |

REG_SP_INT_CTRL

Name : SPORT Interrupt Control Register

Size : 32

Address offset : 00Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:24 |

INT_ENABLE_DSP_1 |

R/W |

0x0 |

Bit[24]: for the interrupt of “sp_ready_to_tx_1” Bit[25]: for the interrupt of “sp_ready_to_rx_1” Bit[26]: for the interrupt of “tx_fifo_full_intr_1” Bit[27]: for the interrupt of “rx_fifo_full_intr_1” Bit[28]: for the interrupt of “tx_fifo_empty_intr_1” Bit[29]: for the interrupt of “rx_fifo_empty_intr_1” Bit[30]: for the interrupt of “tx_i2s_idle_1” Bit[31]: Reserved |

23:16 |

INT_ENABLE_DSP_0 |

R/W |

0x0 |

Bit[16]: for the interrupt of “sp_ready_to_tx” Bit[17]: for the interrupt of “sp_ready_to_rx” Bit[18]: for the interrupt of “tx_fifo_full_intr” Bit[19]: for the interrupt of “rx_fifo_full_intr” Bit[20]: for the interrupt of “tx_fifo_empty_intr” Bit[21]: for the interrupt of “rx_fifo_empty_intr” Bit[22]: for the interrupt of “tx_i2s_idle” Bit[23]: Reserved |

15:14 |

DUMMY |

R/W |

0x0 |

- |

13:9 |

INTR_CLR_1 |

R/W |

0x0 |

Bit[9]: for the interrupt of “tx_fifo_full_intr_1” Bit[10]: for the interrupt of “rx_fifo_full_intr_1” Bit[11]: for the interrupt of “tx_fifo_empty_intr_1” Bit[12]: for the interrupt of “rx_fifo_empty_intr_1” Bit[13]: Reserved |

8 |

RX_DSP_CLEAR_INT_1 |

R/W |

0 |

For DSP mode (bypass GDMA), F/W writes 1’b1 and then 1’b0 to clear Rx interrupt. Note Rx interrupt is to indicate that DSP can get audio data f rom RX_FIFO_1. |

7 |

TX_DSP_CLEAR_INT_1 |

R/W |

0 |

For DSP mode (bypass GDMA), F/W writes 1’b1 and then 1’b0 to clear TX interrupt. Note Tx interrupt is to indicate that DSP can write audio data to TX_FIFO_1. |

6:2 |

INTR_CLR_0 |

R/W |

0x0 |

Bit[2]: for the interrupt of “tx_fifo_full_intr” Bit[3]: for the interrupt of “rx_fifo_full_intr” Bit[4]: for the interrupt of “tx_fifo_empty_intr” Bit[5]: for the interrupt of “rx_fifo_empty_intr” Bit[6]: Reserved |

1 |

RX_DSP_CLEAR_INT_0 |

R/W |

0 |

For DSP mode (bypass GDMA), F/W writes 1’b1 and then 1’b0 to clear Rx interrupt. Note Rx interrupt is to indicate that DSP can get audio data f rom RX_FIFO_0. |

0 |

TX_DSP_CLEAR_INT_0 |

R/W |

0 |

For DSP mode (bypass GDMA), F/W writes 1’b1 and then 1’b0 to clear Tx interrupt. Note Tx interrupt is to indicate that DSP can write audio data to TX_FIFO_0. |

REG_SP_TRX_COUNTER_STATUS

Name : SPORT TRX Counter Status Register

Size : 32

Address offset : 014h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

SP_RESET_STATE |

R |

0 |

1’b1: sp_reset is enabled. 1’b0: sp_reset is disabled. |

30 |

RSVD |

R |

- |

Reserved |

29:24 |

RX_DEPTH_CNT_1 |

R |

0x0 |

RX_FIFO_1 depth counter status (MIC path) |

23:22 |

RSVD |

R |

- |

Reserved |

21:16 |

TX_DEPTH_CNT_1 |

R |

0x0 |

TX_FIFO_1 depth counter status (SPK path) |

15:14 |

RSVD |

R |

- |

Reserved |

13:8 |

RX_DEPTH_CNT_0 |

R |

0x0 |

RX_FIFO_0 depth counter status (MIC path) |

7:6 |

RSVD |

R |

- |

Reserved |

5:0 |

TX_DEPTH_CNT_0 |

R |

0x0 |

TX_FIFO_0 depth counter status (SPK path) |

REG_SP_ERR

Name : SPORT Error Register

Size : 32

Address offset : 018h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:16 |

RX_ERR_CNT |

R |

0x0 |

Rx error counter (MIC path) Note This counter should always be zero if everything works we ll. |

15:0 |

TX_ERR_CNT |

R |

0x0 |

Tx error counter (SPK path) Note This counter should always be zero if everything works we ll. |

REG_SR_TX_BCLK

Name : SPORT Tx BCLK Register

Size : 32

Address offset : 01Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

TX_MI_NI_UPDATE |

R/W |

0 |

1’b1: to update “mi” and “ni” to get the new clock rate. This bit will be reset automatically when the update is done |

30:16 |

TX_NI |

R/W |

0x30 |

BCLK = 40MHz*(ni/mi) For example: BCLK=3.072MHz=40MHz*(48/625) |

15:0 |

TX_MI |

R/W |

0x271 |

REG_SP_TX_LRCLK

Name : SPORT Tx LRCLK Register

Size : 32

Address offset : 020h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:24 |

RX_BCLK_DIV_RATIO |

R/W |

0x3F |

Rx bclk even-bit integer divider. Used in “mode_40mhz” set as 1’b1. (rx_bclk_div_ratio + 1) is the number of “sck_out” cycles wi thin a “ws_out_rx” cycle (1/fs). Default of (rx_bclk_div_ratio + 1) is 64. Set as 64 – 1 = 63 . Only odd number supported. Maximum is 255. |

23:16 |

TX_BCLK_DIV_RATIO |

R/W |

0x3F |

Tx bclk even-bit integer divider. Used in “mode_40mhz” set as 1’b1. (tx_bclk_div_ratio + 1) is the number of “sck_out” cycles wi thin a “ws_out_tx” cycle (1/fs). Default of (tx_bclk_div_ratio + 1) is 64. Set as 64 – 1 = 63 . Only odd number supported. Maximum is 255. |

15:14 |

DUMMY1 |

R/W |

0x0 |

- |

13:8 |

RXDMA_BUSRTSIZE |

R/W |

0x10 |

Rx DMA burst size |

7:6 |

DUMMY2 |

R/W |

0x0 |

- |

5:0 |

TXDMA_BURSTSIZE |

R/W |

0x10 |

Tx DMA burst size |

REG_SP_FIFO_CTRL

Name : SPORT FIFO Control Register

Size : 32

Address offset : 024h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

RX_FIFO_EMPTY_0 |

R |

1 |

|

30 |

TX_FIFO_EMPTY_0 |

R |

1 |

|

29 |

RX_FIFO_FULL_0 |

R |

0 |

|

28 |

TX_FIFO_FULL_0 |

R |

0 |

|

27 |

RX_FIFO_EMPTY_1 |

R |

1 |

|

26 |

TX_FIFO_EMPTY_1 |

R |

1 |

|

25 |

RX_FIFO_FULL_1 |

R |

0 |

|

24 |

TX_FIFO_FULL_1 |

R |

0 |

|

23:14 |

RSVD |

R |

- |

Reserved |

13 |

TX_I2S_IDLE_1 |

R |

0 |

|

12 |

RX_FIFO_EMPTY_INTR_1 |

R |

0 |

|

11 |

TX_FIFO_EMPTY_INTR_1 |

R |

0 |

|

10 |

RX_FIFO_FULL_INTR_1 |

R |

0 |

|

9 |

TX_FIFO_FULL_INTR_1 |

R |

0 |

|

8 |

SP_READY_TO_RX_1 |

R |

0 |

|

7 |

SP_READY_TO_TX_1 |

R |

0 |

|

6 |

TX_I2S_IDLE_0 |

R |

0 |

|

5 |

RX_FIFO_EMPTY_INTR_0 |

R |

0 |

|

4 |

TX_FIFO_EMPTY_INTR_0 |

R |

0 |

|

3 |

RX_FIFO_FULL_INTR_0 |

R |

0 |

|

2 |

TX_FIFO_FULL_INTR_0 |

R |

0 |

|

1 |

SP_READY_TO_RX_0 |

R |

0 |

|

0 |

SP_READY_TO_TX_0 |

R |

0 |

|

REG_SP_FORMAT

Name : SPORT Format Register

Size : 32

Address offset : 028h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

TRX_SAME_CH_LEN |

R/W |

0 |

|

30:28 |

SP_CH_LEN_SEL_RX |

R/W |

0x4 |

3’b000: 16 bits 3’b001: 20 bits 3’b010: 24 bits 3’b100: 32 bits |

27 |

DUMMY3 |

R/W |

0 |

- |

26:24 |

SP_CH_LEN_SEL_TX |

R/W |

0x4 |

3’b000: 16 bits 3’b001: 20 bits 3’b010: 24 bits 3’b100: 32 bits |

23 |

RX_IDEAL_LEN_EN |

R/W |

0 |

Function enable of rx_ideal_len. |

22:20 |

RX_IDEAL_LEN |

R/W |

0x0 |

Sd_in can be received 1 ~ 8 ( = rx_ideal_len + 1 ) BCLK cycl e latter. |

19 |

TX_IDEAL_LEN_EN |

R/W |

0 |

Function enable of tx_ideal_len. PCMA SDO will be delayed 1 LRCK. |

18:16 |

TX_IDEAL_LEN |

R/W |

0x0 |

Sd_out can be sent 1 ~ 8 ( = tx_ideal_len + 1 ) BCLK cycle e arlier. |

15 |

DUMMY4 |

R/W |

0 |

- |

14:12 |

SP_DATA_LEN_SEL_RX_0 |

R/W |

0x0 |

Data length of MIC path and it is valid if “trx_same_length” == 1’b0. 3’b000: 16 bits 3’b001: 20 bits 3’b010: 24 bits 3’b100: 32 bits |

11 |

SP_EN_I2S_MONO_RX_0 |

R/W |

0 |

Channel format of MIC path and it is valid if “trx_same_ch” == 1’b0.

|

10 |

TRX_SAME_LRC |

R/W |

0 |

|

9:8 |

SP_DATA_FORMAT_SEL_RX |

R/W |

0x0 |

Data format of MIC path and it is valid if “trx_same_fs” == 1’b0. 2’b00: I2S 2’b01: Left-justified 2’b10: PCM mode A 2’b11: PCM mode B |

7 |

FIXED_BCLK |

R/W |

0 |

|

6 |

FIXED_BCLK_SEL |

R/W |

0 |

|

5 |

SP_WCLK_RX_INVERSE |

R/W |

0 |

|

4 |

DUMMY5 |

R/W |

0 |

- |

3 |

SCK_OUT_INVERSE |

R/W |

0 |

|

2 |

TRX_SAME_LENGTH |

R/W |

1 |

Both are either 16 or 24 bits |

1 |

TRX_SAME_CH |

R/W |

1 |

Both are either stereo or mono |

0 |

TRX_SAME_FS |

R/W |

1 |

|

REG_SP_RX_BCLK

Name : SPORT Rx BCLK Register

Size : 32

Address offset : 02Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

RX_MI_NI_UPDATE |

R/W |

0 |

1’b1: to update “mi” and “ni” to get the new clock rate. This bit will be reset automatically when the update is done |

30:16 |

RX_NI |

R/W |

0x30 |

BCLK = 40MHz*(ni/mi) For example: BCLK=3.072MHz=40MHz*(48/625) |

15:0 |

RX_MI |

R/W |

0x271 |

REG_SP_RX_LRCLK

Name : SPORT Rx LRCLK Register

Size : 32

Address offset : 030h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

CLR_TX_SPORT_RDY |

R/W |

0 |

For read, the read data is from clr_tx_sport_rdy |

30 |

EN_TX_SPORT_INTERRUPT |

R/W |

0 |

Enable tx_sport_interrupt |

29 |

EN_FS_PHASE_LATCH |

R/W |

0 |

This control bit is “write 1 clear” type |

28:27 |

DUMMY6 |

R/W |

0x0 |

|

26:0 |

TX_SPORT_COMPARE_VAL |

R/W |

0x40 |

X = (tx_sport_compare_val). When counter equal X. SPORT will send tx_sport_interrupt to DSP. FW should take care X={32~134217727} |

REG_SP_DSP_COUNTER

Name : SPORT DSP Counter Register

Size : 32

Address offset : 034h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:5 |

TX_SPORT_COUNTER |

R |

0x0 |

For DSP read instant Tx SPORT counter value, counter down |

4:0 |

TX_FS_PHASE_RPT |

R |

0x0 |

Report Tx phase |

REG_SP_DIRECT_CTRL0

Name : SPORT Direct Control Register 0

Size : 32

Address offset : 03Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:28 |

TX_CH7_DATA_SEL |

R/W |

0x7 |

4’h0: tx_fifo_0_reg_0_l 4’h1: tx_fifo_0_reg_0_r 4’h2: tx_fifo_0_reg_1_l 4’h3: tx_fifo_0_reg_1_r 4’h4: tx_fifo_1_reg_0_l 4’h5: tx_fifo_1_reg_0_r 4’h6: tx_fifo_1_reg_1_l 4’h7: tx_fifo_1_reg_1_r 4’h8: direct_reg_7 |

27:24 |

TX_CH6_DATA_SEL |

R/W |

0x6 |

4’h8: direct_reg_6 |

23:20 |

TX_CH5_DATA_SEL |

R/W |

0x5 |

4’h8: direct_reg_5 |

19:16 |

TX_CH4_DATA_SEL |

R/W |

0x4 |

4’h8: direct_reg_4 |

15:12 |

TX_CH3_DATA_SEL |

R/W |

0x3 |

4’h8: direct_reg_3 |

11:8 |

TX_CH2_DATA_SEL |

R/W |

0x2 |

4’h8: direct_reg_2 |

7:4 |

TX_CH1_DATA_SEL |

R/W |

0x1 |

4’h8: direct_reg_1 |

3:0 |

TX_CH0_DATA_SEL |

R/W |

0x0 |

4’h8: direct_reg_0 |

REG_SP_FIFO_IRQ

Name : SPORT FIFO IRQ Register

Size : 32

Address offset : 044h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

RX_LSB_FIRST_1 |

R/W |

0 |

1’b0: MSB first when Tx 1’b1: LSB first |

30 |

TX_LSB_FIRST_1 |

R/W |

0 |

1’b0: MSB first when Tx 1’b1: LSB first |

29 |

RX_SNK_LR_SWAP_1 |

R/W |

0 |

1’b1: swap L/R audio samples written to the sink memory of R X_FIFO_1 |

28 |

RX_SNK_BYTE_SWAP_1 |

R/W |

0 |

1’b1: swap H/L bytes written to the sink memory of RX_FIFO_1 |

27 |

TX_SRC_LR_SWAP_1 |

R/W |

0 |

1’b1: swap L/R audio samples read from the source memory of TX_FIFO_1 |

26 |

TX_SRC_BYTE_SWAP_1 |

R/W |

0 |

1’b1: swap H/L bytes read from the source memory of TX_FIFO_ 1 |

25:16 |

DUMMY7 |

R/W |

0x0 |

- |

15:8 |

INT_ENABLE_MCU_1 |

R/W |

0x0 |

Bit8]: for the interrupt of “sp_ready_to_tx” Bit9]: for the interrupt of “sp_ready_to_rx” Bit10]: for the interrupt of “tx_fifo_full_intr” Bit11]: for the interrupt of “rx_fifo_full_intr” Bit12]: for the interrupt of “tx_fifo_empty_intr” Bit13]: for the interrupt of “rx_fifo_empty_intr” Bit14]: for the interrupt of “tx_i2s_idle” Bit15]: reserved |

7:0 |

INT_ENABLE_MCU_0 |

R/W |

0x0 |

Bit0]: for the interrupt of “sp_ready_to_tx” Bit1]: for the interrupt of “sp_ready_to_rx” Bit2]: for the interrupt of “tx_fifo_full_intr” Bit3]: for the interrupt of “rx_fifo_full_intr” Bit4]: for the interrupt of “tx_fifo_empty_intr” Bit5]: for the interrupt of “rx_fifo_empty_intr” Bit6]: for the interrupt of “tx_i2s_idle” Bit7]: reserved |

REG_SP_DIRECT_CTRL1

Name : SPORT Direct Control Register 1

Size : 32

Address offset : 048h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

SP_EN_I2S_MONO_RX_1 |

R/W |

0 |

Channel format of MIC path and it is valid if “trx_same_ch” == 1’b0. 1’b1: mono 1’b0: stereo |

30:28 |

SP_DATA_LEN_SEL_RX_1 |

R/W |

0x0 |

Data length of MIC path and it is valid if “trx_same_length” == 1’b0. 3’b000: 16 bits 3’b001: 20 bits 3’b010: 24 bits 3’b100: 32 bits |

27 |

SP_EN_I2S_MONO_TX_1 |

R/W |

0 |

1’b1: mono 1’b0: stereo |

26:24 |

SP_DATA_LEN_SEL_TX_1 |

R/W |

0x0 |

3’b000: 16 bits 3’b001: 20 bits 3’b010: 24 bits 3’b100: 32 bits |

23 |

DIRECT_REG_3_EN |

R/W |

0 |

1’b1: Enable direct_reg_3. |

22:18 |

DIRECT_REG_3_SEL |

R/W |

0x0 |

5’h0: spa_direct_in_0 5’h1: spa_direct_in_1 5’h2: spa_direct_in_2 5’h3: spa_direct_in_3 5’h4: spa_direct_in_4 5’h5: spa_direct_in_5 5’h6: spa_direct_in_6 5’h7: spa_direct_in_7 5’h8: spb_direct_in_0 5’h9: spb_direct_in_1 5’ha: spb_direct_in_2 5’hb: spb_direct_in_3 5’hc: spb_direct_in_4 5’hd: spb_direct_in_5 5’he: spb_direct_in_6 5’hf: spb_direct_in_7 5’h10: spc_direct_in_0 5’h11: spc_direct_in_1 5’h12: spc_direct_in_2 5’h13: spc_direct_in_3 5’h14: spc_direct_in_4 5’h15: spc_direct_in_5 5’h16: spc_direct_in_6 5’h17: spc_direct_in_7 5’h18: sp0_direct_in_tx_fifo_0_reg_0_l 5’h19: sp0_direct_in_tx_fifo_0_reg_0_r 5’h1a: sp0_direct_in_tx_fifo_0_reg_1_l 5’h1b: sp0_direct_in_tx_fifo_0_reg_1_r 5’h1c: TDM_RX_CH3 SPORT0: a = 1, b = 2, c = 3 SPORT1: a = 0, b = 2, c = 3 SPORT2: a = 0, b = 1, c = 3 SPORT3: a = 0, b = 1, c = 2 |

17 |

DIRECT_REG_2_EN |

R/W |

0 |

1’b1: Enable direct_reg_2. |

16:12 |

DIRECT_REG_2_SEL |

R/W |

0x0 |

5’h1c: TDM_RX_CH2 |

11 |

DIRECT_REG_1_EN |

R/W |

0 |

1’b1: Enable direct_reg_1. |

10:6 |

DIRECT_REG_1_SEL |

R/W |

0x0 |

5’h1c: TDM_RX_CH1 |

5 |

DIRECT_REG_0_EN |

R/W |

0 |

1’b1: Enable direct_reg_0. |

4:0 |

DIRECT_REG_0_SEL |

R/W |

0x0 |

5’h1c: TDM_RX_CH0 |

REG_SP_DIRECT_CTRL2

Name : SPORT Direct Control Register 2

Size : 32

Address offset : 04Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

SP_DIRECT_OUT_7_EN |

R/W |

0 |

Enable sp_direct_out_7. |

30 |

SP_DIRECT_OUT_6_EN |

R/W |

0 |

Enable sp_direct_out_6. |

29 |

SP_DIRECT_OUT_5_EN |

R/W |

0 |

Enable sp_direct_out_5. |

28 |

SP_DIRECT_OUT_4_EN |

R/W |

0 |

Enable sp_direct_out_4. |

27 |

SP_DIRECT_OUT_3_EN |

R/W |

0 |

Enable sp_direct_out_3. |

26 |

SP_DIRECT_OUT_2_EN |

R/W |

0 |

Enable sp_direct_out_2. |

25 |

SP_DIRECT_OUT_1_EN |

R/W |

0 |

Enable sp_direct_out_1. |

24 |

SP_DIRECT_OUT_0_EN |

R/W |

0 |

Enable sp_direct_out_0. |

23 |

DIRECT_REG_7_EN |

R/W |

0 |

1’b1: Enable direct_reg_7. |

22:18 |

DIRECT_REG_7_SEL |

R/W |

0x0 |

5’h0: spa_direct_in_0 5’h1: spa_direct_in_1 5’h2: spa_direct_in_2 5’h3: spa_direct_in_3 5’h4: spa_direct_in_4 5’h5: spa_direct_in_5 5’h6: spa_direct_in_6 5’h7: spa_direct_in_7 5’h8: spb_direct_in_0 5’h9: spb_direct_in_1 5’ha: spb_direct_in_2 5’hb: spb_direct_in_3 5’hc: spb_direct_in_4 5’hd: spb_direct_in_5 5’he: spb_direct_in_6 5’hf: spb_direct_in_7 5’h10: spc_direct_in_0 5’h11: spc_direct_in_1 5’h12: spc_direct_in_2 5’h13: spc_direct_in_3 5’h14: spc_direct_in_4 5’h15: spc_direct_in_5 5’h16: spc_direct_in_6 5’h17: spc_direct_in_7 5’h18: sp0_direct_in_tx_fifo_0_reg_0_l 5’h19: sp0_direct_in_tx_fifo_0_reg_0_r 5’h1a: sp0_direct_in_tx_fifo_0_reg_1_l 5’h1b: sp0_direct_in_tx_fifo_0_reg_1_r 5’h1c: TDM_RX_CH7 SPORT0: a = 1, b = 2, c = 3 SPORT1: a = 0, b = 2, c = 3 SPORT2: a = 0, b = 1, c = 3 SPORT3: a = 0, b = 1, c = 2 |

17 |

DIRECT_REG_6_EN |

R/W |

0 |

1’b1: Enable direct_reg_6. |

16:12 |

DIRECT_REG_6_SEL |

R/W |

0x0 |

5’h1c: TDM_RX_CH6 |

11 |

DIRECT_REG_5_EN |

R/W |

0 |

1’b1: Enable direct_reg_5. |

10:6 |

DIRECT_REG_5_SEL |

R/W |

0x0 |

5’h1c: TDM_RX_CH5 |

5 |

DIRECT_REG_4_EN |

R/W |

0 |

1’b1: Enable direct_reg_4. |

4:0 |

DIRECT_REG_4_SEL |

R/W |

0x0 |

5’h1c: TDM_RX_CH4 |

REG_SP_DIRECT_CTRL3

Name : SPORT Direct Control Register 3

Size : 32

Address offset : 054h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:29 |

DUMMY8 |

R/W |

0x0 |

- |

28:24 |

RX_FIFO_0_REG_1_R_SEL |

R/W |

0x3 |

5’d0: RX_CH0_data_out (MIC path) 5’d1: RX_CH1_data_out (MIC path) 5’d2: RX_CH2_data_out (MIC path) 5’d3: RX_CH3_data_out (MIC path) 5’d4: RX_CH4_data_out (MIC path) 5’d5: RX_CH5_data_out (MIC path) 5’d6: RX_CH6_data_out (MIC path) 5’d7: RX_CH7_data_out (MIC path) 5’d8: spa_direct_in_0 5’d9: spa_direct_in_1 5’d10: spa_direct_in_2 5’d11: spa_direct_in_3 5’d12: spa_direct_in_4 5’d13: spa_direct_in_5 5’d14: spa_direct_in_6 5’d15: spa_direct_in_7 5’d16: spb_direct_in_0 5’d17: spb_direct_in_1 5’d18: spb_direct_in_2 5’d19: spb_direct_in_3 5’d20: spb_direct_in_4 5’d21: spb_direct_in_5 5’d22: spb_direct_in_6 5’d23: spb_direct_in_7 5’d24: spc_direct_in_0 5’d25: spc_direct_in_1 5’d26: spc_direct_in_2 5’d27: spc_direct_in_3 5’d28: spc_direct_in_4 5’d29: spc_direct_in_5 5’d30: spc_direct_in_6 5’d31: spc_direct_in_7 SPORT0: a = 1, b = 2, c = 3 SPORT1: a = 0, b = 2, c = 3 SPORT2: a = 0, b = 1, c = 3 SPORT3: a = 0, b = 1, c = 2 |

23:21 |

DUMMY9 |

R/W |

0x0 |

|

20:16 |

RX_FIFO_0_REG_1_L_SEL |

R/W |

0x2 |

|

15:13 |

DUMMY10 |

R/W |

0x0 |

|

12:8 |

RX_FIFO_0_REG_0_R_SEL |

R/W |

0x1 |

|

7:5 |

DUMMY11 |

R/W |

0x0 |

|

4:0 |

RX_FIFO_0_REG_0_L_SEL |

R/W |

0x0 |

REG_SP_DIRECT_CTRL4

Name : SPORT Direct Control Register 4

Size : 32

Address offset : 058h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:29 |

DUMMY12 |

R/W |

0x0 |

|

28:24 |

RX_FIFO_1_REG_1_R_SEL |

R/W |

0x7 |

5’d0: RX_CH0_data_out (MIC path) 5’d1: RX_CH1_data_out (MIC path) 5’d2: RX_CH2_data_out (MIC path) 5’d3: RX_CH3_data_out (MIC path) 5’d4: RX_CH4_data_out (MIC path) 5’d5: RX_CH5_data_out (MIC path) 5’d6: RX_CH6_data_out (MIC path) 5’d7: RX_CH7_data_out (MIC path) 5’d8: spa_direct_in_0 5’d9: spa_direct_in_1 5’d10: spa_direct_in_2 5’d11: spa_direct_in_3 5’d12: spa_direct_in_4 5’d13: spa_direct_in_5 5’d14: spa_direct_in_6 5’d15: spa_direct_in_7 5’d16: spb_direct_in_0 5’d17: spb_direct_in_1 5’d18: spb_direct_in_2 5’d19: spb_direct_in_3 5’d20: spb_direct_in_4 5’d21: spb_direct_in_5 5’d22: spb_direct_in_6 5’d23: spb_direct_in_7 5’d24: spc_direct_in_0 5’d25: spc_direct_in_1 5’d26: spc_direct_in_2 5’d27: spc_direct_in_3 5’d28: spc_direct_in_4 5’d29: spc_direct_in_5 5’d30: spc_direct_in_6 5’d31: spc_direct_in_7 SPORT0: a = 1, b = 2, c = 3 SPORT1: a = 0, b = 2, c = 3 SPORT2: a = 0, b = 1, c = 3 SPORT3: a = 0, b = 1, c = 2 |

23:21 |

DUMMY13 |

R/W |

0x0 |

|

20:16 |

RX_FIFO_1_REG_1_L_SEL |

R/W |

0x6 |

|

15:13 |

DUMMY14 |

R/W |

0x0 |

|

12:8 |

RX_FIFO_1_REG_0_R_SEL |

R/W |

0x5 |

|

7:5 |

DUMMY15 |

R/W |

0x0 |

|

4:0 |

RX_FIFO_1_REG_0_L_SEL |

R/W |

0x4 |

REG_SP_RX_COUNTER1

Name : SPORT Rx Counter Register 1

Size : 32

Address offset : 05Ch

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

CLR_RX_SPORT_RDY |

R/W |

0 |

X = (tx_sport_compare_val). When counter equal X. SPORT will send tx_sport_interrupt to DSP. FW should take care X={32~8191} |

30 |

EN_RX_SPORT_INTERRUPT |

R/W |

0 |

Enable rx sport interrupt. |

29:27 |

DUMMY16 |

R/W |

0x0 |

|

26:0 |

RX_SPORT_COMPARE_VAL |

R/W |

0x40 |

X = (rx_sport_compare_val). When counter equal X. SPORT will send rx_sport_interrupt to DSP. FW should take care X={32~134217727} |

REG_SP_RX_COUNTER2

Name : SPORT Rx Counter Register 2

Size : 32

Address offset : 060h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:5 |

RX_SPORT_COUNTER |

R |

0x0 |

For DSP read instant Rx SPORT counter value, counter down |

4:0 |

RX_FS_PHASE_RPT |

R |

0x0 |

Report Rx phase |

REG_SP_MCLK

Name : SPORT MCLK Register

Size : 32

Address offset : 064h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

MCLK_MI_NI_UPDATE |

R/W |

0 |

1’b1: to update “mi” and “ni” to get the new clock rate. This bit will be reset automatically when the update is done |

30:16 |

MCLK_NI |

R/W |

0xc0 |

Mclk_out = 40MHz*(ni/mi) For example: mclk_out=3.072MHz=40MHz*(48/625) |

15:0 |

MCLK_MI |

R/W |

0x271 |

REG_TX_FIFO_0_WR_ADDR

Name : TX FIFO 0 Write Address Register

Size : 32

Address offset : 800h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

TX_FIFO_0_WR_ADDR |

R/W |

0x0 |

TX_FIFO_0 write address |

REG_RX_FIFO_0_RD_ADDR

Name : RX FIFO 0 Read Address Register

Size : 32

Address offset : 880h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

RX_FIFO_0_RD_ADDR |

R |

0x0 |

RX_FIFO_0 read address |

REG_TX_FIFO_1_WR_ADDR

Name : TX FIFO 1 Write Address Register

Size : 32

Address offset : 900h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

TX_FIFO_1_WR_ADDR |

R/W |

0x0 |

TX_FIFO_1 write address |

REG_RX_FIFO_1_RD_ADDR

Name : RX FIFO 1 Read Address Register

Size : 32

Address offset : 980h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

RX_FIFO_1_RD_ADDR |

R |

0x0 |

RX_FIFO_1 read address |

Base Address:

SPORT0_REG : 0x4011C000

SPORT1_REG : 0x4011D000

Name |

Address offset |

Access |

Description |

|---|---|---|---|

000h |

R/W |

||

004h |

R/W |

||

008h |

R/W |

||

00Ch |

R/W |

||

014h |

R |

||

018h |

R |

||

01Ch |

R/W |

||

020h |

R/W |

||

024h |

R |

||

028h |

R/W |

||

02Ch |

R/W |

||

030h |

R/W |

||

034h |

R |

||

03Ch |

R/W |

||

044h |

R/W |

||

048h |

R/W |

||

04Ch |

R/W |

||

054h |

R/W |

||

058h |

R/W |

||

05Ch |

R/W |

||

060h |

R |

||

800h |

R/W |

||

880h |

R |

||

900h |

R/W |

||

980h |

R |

REG_SP_REG_MUX

Name : SPORT MUX Register

Size : 32

Address offset : 000h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

SP_REG_MUX |

R/W |

0xFFFFFFFF |

Mux of register write with different base address of the sam e SPORT. This register can be set as different value with four differ ent base address in one SPORT, but other registers share the same value with four different base addresses in one SPORT. |

REG_SP_CTRL0

Name : SPORT Control Register 0

Size : 32

Address offset : 004h

Read/write access : R/W

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:30 |

MCLK_SEL |

R/W |

0x0 |

2’b00: MCLK output=dsp_src_clk/4 2’b01: MCLK output=dsp_src_clk/2 2’b10/2’b11: MCLK output=dsp_src_clk |

29:28 |

SP_SEL_I2S_RX_CH |

R/W |

0x0 |

ADC path 2’b00: L/R 2’b01: R/L 2’b10: L/L 2’b11: R/R |

27:26 |

SP_SEL_I2S_TX_CH |

R/W |

0x0 |

DAC path 2’b00: L/R 2’b01: R/L 2’b10: L/L 2’b11: R/R |

25 |

SP_START_RX |

R/W |

0 |

1’b0: Rx is disabled. 1’b1: Rx is started. |

24 |

SP_RX_DISABLE |

R/W |

1 |

1’b1: SPORT Rx is disabled. 1’b0: SPORT Rx is enabled. |

23 |

RX_LSB_FIRST_0 |

R/W |

0 |

1’b0: MSB first when Rx 1’b1: LSB first |

22 |

TX_LSB_FIRST_0 |

R/W |

0 |

1’b0: MSB first when Tx 1’b1: LSB first |

21:20 |

SP_TDM_MODE_SEL_RX |

R/W |

0x0 |

2’b00: Without TDM 2’b01: TDM4 2’b10: TDM6 2’b11: TDM8 |

19:18 |

SP_TDM_MODE_SEL_TX |

R/W |

0x0 |

2’b00: Without TDM 2’b01: TDM4 2’b10: TDM6 2’b11: TDM8 |

17 |

SP_START_TX |

R/W |

0 |

1’b0: Tx is disabled. 1’b1: Tx is started. |

16 |

SP_TX_DISABLE |

R/W |

1 |

1’b1: SPORT Tx is disabled. 1’b0: SPORT Tx is enabled. |

15 |

SP_I2S_SELF_LPBK_EN |

R/W |

0 |

1’b1: internal loopback mode is enabled. |

14:12 |

SP_DATA_LEN_SEL_TX_0 |

R/W |

0x0 |

3’b000: 16 bits 3’b001: 20 bits 3’b010: 24 bits 3’b100: 32 bits |

11 |

SP_EN_I2S_MONO_TX_0 |

R/W |

0 |

1’b1: mono 1’b0: stereo |

10 |

SP_INV_I2S_SCLK |

R/W |

0 |

1’b1: I2S/PCM bit clock is inverted. |

9:8 |

SP_DATA_FORMAT_SEL_TX |

R/W |

0x0 |

2’b00: I2S 2’b01: Left-justified 2’b10: PCM mode A 2’b11: PCM mode B |

7 |

DSP_CTL_MODE |

R/W |

0 |

1’b1: DSP and SPORT1 handshaking is enabled. 1’b0: GDMA and SPORT1 handshaking is enabled. |

6 |

SP_LOOPBACK |

R/W |

0 |

1’b1: Self-loopback mode |

5 |

SP_WCLK_TX_INVERSE |

R/W |

0 |

1’b1: I2S/PCM word clock is inverted for Tx (SPK path) |

4 |

SLAVE_DATA_SEL |

R/W |

0 |

1’b1: To be an I2S or PCM slave (data path) |

3 |

SLAVE_CLK_SEL |

R/W |

0 |

1’b1: To be an I2S or PCM slave (CLK path) |

2 |

RX_INV_I2S_SCLK |

R/W |

0 |

|