Power Management

Power Architecture

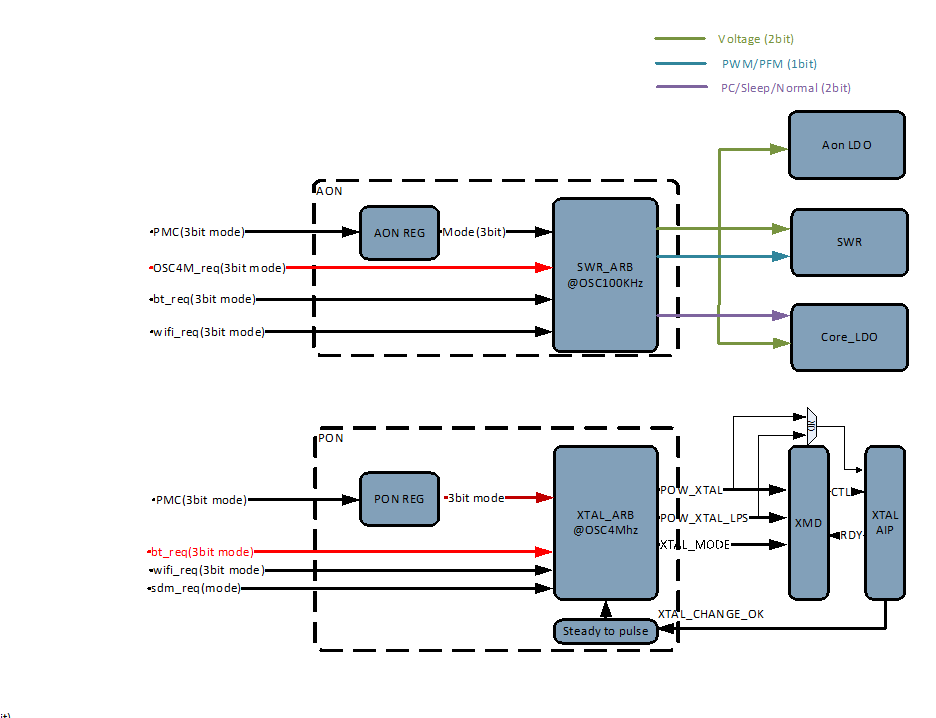

The power architecture is shown below.

LDO_AON: 0.7V/0.8V

SWR: 1.25V

LDO_Core: 0.7V/0.8V (sleep), 0.9V/1V (active)

LDO_1.8V: 1.8V for Audio Analog and PSRAM

Power Architecture

Power Cut control

Syson power cut control is shown below.

Note

BT_PMC工作在 BTON domain, 所以无法控制 PC1

RSIP/SPIC platform 等 control register 有采用 retention flip-flop 的方式, 在 chip 所选制程和 Cell 下, 每个 retention bits penalty current 为 30pw.

Power cut |

Controller |

Enable |

Disable |

|---|---|---|---|

PC0 |

WIFI PMC & BT PMC |

BT PMC的request or WIFI PMC的request |

WIFI PMC request和BT PMC同时request |

PC1 |

SW |

SW的request |

SW的request |

PC2 |

WIFI PMC & Syson PMC |

Syson PMC的request or WIFI PMC的request |

Syson PMC request和WIFI PMC同时request |

Aon Power Cut Control

OTP power Cut 完全由HW控制, 在进入和退出 sleep mode 时, 分别由 PMC 控制关闭和打开.

Power cut |

Controller |

Enable |

Disable |

|---|---|---|---|

PC3 |

PMC |

Aon PMC or LP PMC 在power on 或者退出sleep时 request |

LP PMC 在进入Sleep的时候 |

Clock Control

Power control |

Clock control |

Reset control |

||

|---|---|---|---|---|

Power on / Wake from dslp |

KM0 |

PMC |

PMC |

PMC |

Power on / Wake from dslp |

KM4 |

PMC |

PMC |

PMC |

Wake from PG |

KM0 |

PMC |

PMC |

PMC |

Wake from PG |

KM4 |

PMC |

KM0 |

PMC |

Wake from CG |

KM0 |

– |

PMC |

– |

Wake from CG |

KM4 |

– |

KM0 |

– |

Note

Syson PMC 仅仅在 initial boot 的时候控制 reg2

Power on flow

Power on/wake from dslp

Power on 或者 wake from dslp 时, PMC 帮忙给 SOC domain 开电, 打开PLL, Enable KM0 和 KM4 的clock, 放开KM0 和KM4的reset.KM0 默认会被halt住, 在KM4 配置好platform security control 以后, 再放开KM0 halt信号

Wake from sleep (PG)

Wake from sleep时, PMC帮忙给SOC domain开电, PMC使能KM0并放开KM0的clock, KM0 Wake 后会根据唤醒源看是否需要给KM4开clock

Sleep Flow (PG)

KM0 sleep 时, PMC帮忙disable KM0 clock, clear KM0 和KM4 的reset (function disable) , 然后关闭SOC domain的 power cut

Wake from sleep (CG)

Wake from sleep时, PMC放开KM0的clock, KM0 Wake 后会根据唤醒源看是否需要给KM4开clock.

Sleep Flow (CG)

KM0 sleep 时, PMC帮忙disable KM0 Clock, 不控制SOC power Domain的power

Note

PLL、CPU 默认init power on工作频率祥见 hspec 下

clock info 这里需提供链接文档, KM0 wake以后工作在Xtal clock,

LDO_1.8V

LDO_1.8V power system is shown below.

LDO_1.8V 共有3种工作mode, 两级dummy load, 其负载能力如下. 两种mode分别对应的使用场景为, 只有flash or psram使用LDO_1.8V , flash 和pram 同时使用LDO_1.8V.

Mode |

MIN(A) |

MAX(A) |

|---|---|---|

sleep mode |

1.00E-06 |

5.00E-03 |

normal mode1 |

2.00E-04 |

6.00E-02 |

normal mode2 |

5.00E-04 |

1.10E-01 |

Dummy load |

Loading |

|---|---|

Level1 |

2.00E-04 |

Level2 |

5.00E-04 |

Note

LDO_1.8V 开关控制需要由HW PMC完成 (默认打开到normal mode1, 并使能Level1的dummy loading) .

Power on/wake from dslp

PMC帮忙Enable LDO_1.8V, 该 LDO 可能会给Flash供电, 在放开CPU的reset前, 需要保证LDO_1.8V 的电压已经上升到

1.8V.Rom code 访问flash 不会做等待上电稳定的动作.Wake or Sleep

Sleep 和wake的时候PMC 会根据configuration 进行对应的关闭和打开

Deepsleep flow

在deep sleep的过程中关闭LDO_1.8V

Note

LDO的控制需要注意dummy loading 和delay, 具体控制注意事项

参考HW power control文档 这里需要指定参考源以便引用在系统sleep状态下, 虽然max current 只有

5.00E-03, 但是HW 认为Psram self-refresh的时间很短, 有外部电容支撑, 可以将此LDO 设定在sleep mode

LDO Control Option

Config |

|

|---|---|

Sleep Dummy Enable |

|

Normal Dummy Enable |

|

Sleep Mode |

|

Normal Mode |

|

Dummy Load Level |

|

HW Global External Interrupt Mask

Interrupt connection in AmebaD这里若替换为chip,无法与下幅图内容区别 is shown below.

在传统的设计中, 中断信号直接接到了NVIC.

当KM4/KM0进sleep之前, 软件会执行 cpsid i 关闭中断 (设置PRIMASK) , 防止在配置sleep的过程中产生中断程序跑乱.但是当CPU执行WFI之后, 就不再看PRIMASK(WFE还是会看PRIMASK).此时CPU就会看到中断, 随后会退出WFI.这时PMC未必能及时gate住CPU, 也可能使得程序跑乱.

Interrupt connection in new design is shown below.

新的设计中, 会将接到NVIC的信号添加一个 GLOBAL_EXT_INT_PRIMASK 逻辑控制. Software 需要在执行cpsid前, 先将INT屏蔽.这时CPU执行WFI以后, PMC可以稳定的gating 住CPU.

Corner Case

以历史芯片出现的corner case 为例, 说明之前问题, 以及我们现在的加强.

AmebaSmart软件flow:

1、软件屏蔽中断 (cpsid)

2、enable硬件屏蔽中断 (

GLOBAL_EXT_INT_PRIMASK)3、write PMC register request进入sleep mode

4、进WFI (如果NVIC上有pending中断, wfi会立马退出, 目前设定pmc看到cpu的sleep状态才会进power off flow, 否则不动)

5、software wake 以后, 执行后续flow.会disable EXT_INT_PRIMASK 硬件屏蔽中断 (该步骤是为了有pending中断, 最终pmc没有进sleep的处理) (这边看起来软件是不是应该补一个清sleep req的动作, 但是目前的hang case看log前面一次有正常sleep)

6、退出sleep mode. Enable irq.

Corner Case 发生的情景

参考 AmebaSmart软件flow step2 的寄存器一旦写好, NVIC的pending int状态是明确的 ( AmebaSmart软件flow step1 和 AmebaSmart软件flow step2 之间可能会发生中断) : 要么就是有pending中断, 要么就是没有中断.根据Pending 状态会有如下两种情景.

Case1: 没有pending 中断, cpu正常进入sleep状态, pmc正常走sleep flow

Case2: 有pending中断, cpu进了wfi后立马退出, 那么cpu的sleep状态是一个小脉冲, 这个小脉冲是给到PMC的一个信号, PMC可能会有正确采到, 和无法正确采集到两种case.

Case2-1: pmc 没采到脉冲, pmc不睡, 软件正常退wfi往下跑, 行为正常

Case2-2: pmc采到了脉冲, pmc正常睡, 此时软件也退了wfi往下跑.PMC sleep的动作可能会降压或者停Clock类动作, 导致非预期现象.

HW Sleep Filter

在 Software 按照 AmebaSmart软件flow step1 和 AmebaSmart软件flow step2 顺序执行, 就会出现 Corner Case 发生的情景case2-2 的非预期状态.这种问题的根本原因是PMC 没有正确的采集到sleep信号的glitch 信号, 因此需要PMC delay sample.

sleep filter illustration

Step1: CPU 执行cpsid disable中断

Step2: 有一外部中断发生, 但是由于PRIMASK , 中断pending bit 置位, CPU不会执行中断

Step3: CPU 通过写 GLOBAL_EXT_INT_PRIMASK 来屏蔽后续中断

Step4: CPU 写 SYSPMC_CTRL 寄存器去trigger PMC为CPU关clock 或者power, 但PMC不会立马执行, 会采集到CPU发出的SLP信号后才会为CPU关闭clock 或者power

Step5: CPU执行WFI, 由于WIF后, CPU会举起SLP 信号.同时PRIMASK会失效 (ARM CPU 特性) .因此pending中断会唤醒CPU, CPU被唤醒后, 会再次拉低sleep信号.导致SLP信号是一个pulse.

Step6: PMC在Delay一定时间 (粒度为若干us.软件可配) 后, 对于SLP信号采样, 这样即使SLP有glitch, 也能够被filter掉.

Step7: Software在被Pending 中断唤醒后, 会继续执行, 并在后续flow中清除对于 SYSPMC_CTRL 的request

Step8: 系统执行后续对应pending中断的handler

Note

在Software 应尽量避免 AmebaSmart软件flow step1 和 AmebaSmart软件flow step2 顺序.需要先设置 GLOBAL_EXT_INT_PRIMASK, 再执行cpsid.但是HW的delay sample 也一定要做, 双重保险.

Wake Event 因为是中断直连过去, 因此此时wake event在此情景下也是可以获取

CG flow

CG suspend flow

KM4 suspend

Step1: KM4 配置wake up source, 并使能该wake up source的INT function.

Step2: KM4在所有的wakelock 都释放的, 然后向KM0发出suspend request, 并进入WFE

Step3: KM0中断中, 将S2 disable, KM4进入CG (

clock_gateKM4) ,并使能KM4_wakeup中断

KM0 suspend

Step1: KM0配置 BIT_LSYS_IRQ_MASK_KM0 mask KM0中断, 向PMC发出CG request, 进入WFI

Step2: PMC将S1 disable, KM0进入CG, PMC配置 BIT_LSYS_IRQ_MASK_KM0 unmask KM0中断

CG resume flow

KM4 resume when KM0 sleep

Step1: PMC收到wake中断, 给KM0开clock

Step2: KM0 wake, 退WFI, 收到

KM4_wakeup中断, 给KM4开clock, 并禁止KM4_wakeup中断, 发送SEV wake KM4Step3: KM4退WFE; 处理 step1 的中断

KM4 resume when KM0 active

Step1: KM0收到

KM4_wakeup中断, KM0给KM4开clock, 并禁止KM4_wakeup中断, 发送SEV wake KM4Step2: KM4退WFE, 处理 step1 的中断

KM0 resume

Step1: PMC收到wake中断, 给KM0开clock

Step2: KM0 wake, 处理 step1 的中断

PG flow

PG suspend flow

KM4 suspend

Step1: KM4 配置wake up source, 并使能该wake up source的INT function.

Step2: KM4在所有的wakelock 都释放的, 然后向KM0发出suspend request, 并进入 WFE

Step3: KM0中断中, 将S2 disable, KM4进入CG (

clock_gateKM4) ,并使能KM4_wakeup中断

Note

Step3 中, 并不用设置 BIT_BOOT_WAKE_FROM_PS_HS, 也不需要控制KM4 的function enable.因为KM0 和KM4 属于同一power domain.在SOC的power确定会被关闭时才需要配置 BIT_BOOT_WAKE_FROM_PS_HS.同时在进退PG时, HW PMC会控制KM4 function enable, 因此KM0 不用控制KM4 function enable

KM0 suspend

Step1: KM0配置 BIT_LSYS_IRQ_MASK_KM0 mask KM0中断, 设置 BIT_BOOT_WAKE_FROM_PS_HS 与 BIT_BOOT_WAKE_FROM_PS_LS.KM4 向PMC发出PG request, PMC disable KM0 clock, KM0进入CG, PMC配置 BIT_LSYS_IRQ_MASK_KM0 unmask KM0中断

Step2: PMC向SOC power的Arbiter发出close SOC power的request, 由Arbiter决定是否关SOC power

Step3: SOC power关闭后, KM0、KM4进入PG

PG resume flow

KM4 resume when KM0 sleep

Step1: PMC收到wake中断, PMC打开SOC的power, 给KM0开clock

Step2: KM0 wake, KM0收到

KM4_wakeup中断, 将S2 enable, 给KM4开clock (clock_onKM4) 并禁止KM4_wakeup中断Step3: KM4 退PG, 处理 step1 的中断

KM4 resume when KM0 active

Step1: KM0收到

KM4_wakeup中断, 将S2 enable, 给KM4开clock (clock_onKM4) , 并禁止KM4_wakeup中断Step2: KM4退PG, 处理 step1 的中断

KM0 resume

Step1: PMC收到wake中断, PMC打开SOC的power, 给KM0开clock

Step2: KM0 退PG, 处理 step1 的中断

Deep Sleep flow

Deep Sleep suspend flow

KM4 suspend

Step1: KM4 配置wake up source, 并使能该wake up source的INT function.

Step2: KM4在所有的wakelock 都释放的, 然后向KM0发出suspend request, 并进入WFE

KM0 suspend

Step1: KM0向PMC发出deep sleep request, PMC Disable LDO_1.8V, PMC Disable SOC power

Step2: Power关闭后, 进入Deepsleep

Deep Sleep resume flow

Sleep Power and Clock Control Flow

KM0/KM4 Wakeup When KM0 Sleep

KM0/KM4 wakeup when PG

KM0/KM4 wakeup when CG

Note

因为KM0和KM4有相同的power domain, 同时开电和断电.因此不支持 (KM4 CG, KM0 PG) (KM4 PG, KM0 CG) 的组合方式, 整个系统应该只有一种sleep mode

Peripherals唤醒KM4步骤:

Step1: Peripheral需要唤醒KM4来处理中断, 需要将此wake source定义为KM4的唤醒源.该中断发生的时候, 会通过 KM4_WAKE_INT 发送给PMC.

Step2: PMC收到 KM4_WAKE_INT 后唤醒KM0, 同时PMC有寄存器知道记录是哪个IP唤醒的系统 (wake event)

Step3: KM0被唤醒之后, 进入 KM4_WAKE_INT 的中断

Step4: KM0在 KM4_WAKE_INT 中为KM4开clock, 同时KM0 Disable KM4_WAKE_INT 中断

Step5: KM4 clock ready后被唤醒

Step6: KM4被唤醒之后处理 Step1 中发出的中断

Peripherals唤醒KM0步骤:

Step1: Peripheral需要唤醒KM0来处理中断, 需要将此wake source定义为KM0的唤醒源.该中断发生的时候这个中断信号会同步发给PMC

Step2: PMC收到这个信号之后唤醒KM0

Step3: KM0被唤醒之后处理 Step1 中发出的中断

KM4 Wakeup When KM0 Active

KM4 PG wakeup when KM0 active

Step1: KM4的某个Peripheral发出中断信号, 由于这时候KM0 处于active状态, 这个信号PMC不会理会

Step2: KM0收到 KM4_WAKE_INT, KM0在中断中为KM4开clock

Step3: KM4 boot 后, 根据PG/CG选择boot flow, 恢复到sleep前的状态

Step4: KM4通过NVIC收到这个中断信号进行处理

Note

实际使用中即使KM4 配置为PG, 但是整个SOC区域没有断过电, KM4 wake的过程中software会走KM4 CG flow.因此KM4 PG的flag 应该只有在KM0 sleep flow的时候配置

KM0 确实进入过PG的情况, KM4的wakeup 一定要走PG wake flow

WoWLAN Resume Flow

WoWLAN中WIFI先唤醒KM0再唤醒KM4的flow is shown below.

Step1: WIFI的TSF early beacon时间到(MAC会有bcn early interrupt送到MAC PMC和系统PMC), 系统PMC发信号唤醒KM0

Step2: SYS PMC会request XTAL, SWR.同时 WIFI PMC会同步request XTAL, SWR, 以及给MAC off 开电, 起req给wlafe pmc去给RF off开电(包括rfafe及rfc)

Step3: 系统PMC收到这个信号后唤醒KM0

Step4: KM0 wake 后, 在early beacon isr中打开BB/RF, 等待接收RX Beacon done中断

Step5: wifi收下beacon且KM0看到beacon TIM IE指示需要跟AP 取缓存包, KM0 发送null0取缓存包, 发现缓存包需要KM4来处理则唤醒KM4, 否则KM0自己release掉收到的beacon以及缓存包后再次sleep下去.

Step6: KM0为KM4开clock

Step7: KM4唤醒, 之后可以处理相关任务

LPS OffLoad Process Flow

LPS Offload process flow is shown below:

Step1: WIFI的TSF early beacon时间到(bcn early interrupt), 会发信号给WIFI PMC.

Step2: MAC PMC 退LPS state回到active, 过程中会request XTAL, SWR, 以及给MAC off 开电, 起req给wlafe pmc去给RF off开电(包括rfafe及rfc)

Step3: bcn early interrupt trigger mac HIOE set RX path ready

Step4: 接收 Beacon 并解析TIM.TIM no hit trigger HIOE set RX path off, 并trigger WIFI PMC再次进入LPS state, 过程中会request XTAL, SWR, 以及给MAC off 关电, 起req给wlafe pmc去给RF off关电(包括rfafe及rfc)

Step5: 如果TIM hit, 或者多次Beacon Timeout, 因MAC相关中断已经连接至系统PMC, 系统会被wake up , KM0会先醒来跑FW处理相关中断, 如判断到需要KM4处理的情况, 再去唤醒KM4, 如无需KM4处理, KM0会set MAC PMC进lps state后KM0随后进入睡眠.

SW trigger wakeup (IPC)

KM0中KM4的唤醒需要同一个Entry, 而不是在软件中直接为KM4开电, 这样很难解决多任务之间的冲突问题, 这个统一entry就是 KM4_WAKE_INT, 所以需要实现Software trigger来触发这两个中断.

KM0可以使用IPC给KM4发送message从而触发自己的 KM4_WAKE_INT 来实现这个功能.KM0唤醒KM4

Note

KM4_WAKE_INT 的中断优先级一定要比IPC的中断优先级低, 因为sleep的flow在IPC中断, wake flow在 KM4_WAKE_INT.sleep flow 不能被wake flow 打断.

KM0 Wakeup KM4 use IPC

Step1: KM0配置

IPC_KM0给IPC_KM4发信息Step2:

IPC_KM0给IPC_KM4发出信息Step3:

IPC_KM4收到信息之后发出Rx中断信号Step4: KM0收到 KM4_WAKE_INT 中断信号

Step5: KM0在中断中为KM4开clock

Step6: KM4被唤醒

Step7: KM4唤醒之后可以处理 step3 中

IPC_KM4发出的中断信号

Wakeup Mask

在说明Wakeup Mask之前, 需要先了解一下各个CPU的中断控制器是如何和每个Peripherals的中断信号连接的, 如下是系统的NVIC diagram:

除了个别peripheral, 大部分peripheral的中断信号是拉给所有CPU的, CPU端的中断控制器决定打开或者关闭这个中断, 客户实际使用时需要保证同一时间只有一个CPU打开了某个peripheral的中断.NVIC的详细信息 请见NVIC Spec此处需提供链接以便跳转, 分配原理如下:

KM0 NVIC |

KM4 NVIC |

|

|---|---|---|

Peripherals |

Y |

Y |

IPC_KM0 |

Y |

|

IPC_KM4 |

Y |

类似NVIC, 所有peripherals的中断信号也会接给wakeup模块, 通过设定特定的mask来决定这个中断信号是唤醒那个系统, 如下是 Wakeup Mask 的diagram:

Wakeup Mask描述如下:

Type |

Comment |

|

|---|---|---|

KM0_WAKE |

Sig |

给到PMC, 用于PMC唤醒KM0 |

KM4_WAKE_INT |

Sig |

给到KM0的NVIC, KM0会在这个IRQ中为KM4开Clock, 其开关方式如下: KM0 Active:

KM0 Sleep:

|

KM0_WAKE_MSK |

Reg |

|

KM4_WAKE_MSK |

Reg |

|

KM0_WAKE_EVENT |

Reg |

每个bit代表一个唤醒源, 详细定义见NVIC table, 所有的wake 信号包括AON_TIM和AON_WAKEPIN都应该在IP端清除event, 而不是靠写wake event寄存器清除, 基于这种设计

|

KM4_WAKE_EVENT |

同上 |

KM0被唤醒的时候会根据收到的中断是 KM4_WAKE 决定是否唤醒KM4

唤醒的时候HW会发哪个中断给KM0是留给客户设置的, 设置的register就是NVIC table中列出的2个 WAKE_MSK: KM0_WAKE_MSK/ KM4_WAKE_MSK, HW会根据这几个MSK决定某个peripheral唤醒的时候发哪个中断

KM0_WAKE_MSK/ KM4_WAKE_MSK 的定义

参考cpu architecture spec中的NVIC table此处需提供链接以便跳转.

Note

KM0_WAKE_MSK 是所有唤醒源的全集, 等于

KM4_WAKE_MSK|其它唤醒信号WAKE_MASK 和 WAKE_EVENT 都放在LPSYSON domain.

WAKE_MASK 和 WAKE_EVENT 超过

32bits时, 应将对应寄存器的bit30和bit31空出,参考RCC寄存器的实现方式此处需提供链接以便跳转.

Wake Event Clear

两个 WAKE_MSK 产生WAKE信号或中断信号时, 都会将 WAKE_EVENT 写到对应的 WAKE_EVENT register中方便软件读取,

WAKE_EVENT 的清除不应该做成是写 WAKE_EVENT register清除, 而是所有的 WAKE_EVENT 清除都应该在IP端清除, 包括

AON_TIM和AON_WAKEPINAmebaD此处不应出现名称``的做法是有些要在IP端清除 (例如UART) , 有些则要通过写 **WAKE_EVENT** register清除 (例如 ``AON_TIM&AON_WAKEPIN) , 这样不利于软件的处理

下面以 AON_TIM 和 AON_WAKEPIN 为例来说明具体的做法:

假设 AON_TIM 和 AON_WAKEPIN 在NVIC注册的中断, 以及每个bitmask的位置如下表所示:

Function |

KM0INT |

KM4INT |

KM0_WAKE_MSK |

KM4_WAKE_MSK |

WAKE_EVENT |

|---|---|---|---|---|---|

AON_TIM |

4 |

79 |

2 |

2 |

2 |

AON_WAKEPIN |

32 |

72 |

37 |

37 |

37 |

对应的原理图如下:

写 WAKE_EVENT register本身不具备清除 PMC_WAKE 信号的能力, 只有收到NVIC中断后, 在中断中通过写 AON_TIM 和 AON_WAKEPIN 的寄存器才能清除这个信号(注意 AmebaD此处不应出现名称 不具备这个功能).

Software Flow<未更新>

software configuration

KM4 suspend时, 将使用PLL的peripheral/SPIC/PSRAM/SRAM/LP clk切到XTAL, 然后关闭PLL

KM4 resume前, 打开PLL, 将peripheral/SPIC/PSRAM/SRAM/LP clk从XTAL切到PLL

KM4 suspend后, 系统这边会request LDO sleep mode + SWR PFM mode

KM4 resume前, 系统会先request LDO normal mode + SWR FWM mdoe

Suspend and resume

HW Sleep filter使用

Interrupt mask使用如下:

先 IRQ_MASK=1, 再 cpisd i

IRQ_MASK 是在cpsid i之后, sleep request之前写 1 的, 对于使用WFI的情况, 会存在 Corner Case 的问题

IRQ_MASK 是在cpsid i之后, sleep request之前写 1 的, 对于使用WFI的情况, 会存在 Corner Case 的问题

IRQ_MASK 是在cpsid i之后, sleep request之前写 1 的, 对于使用WFI的情况, 会存在 Corner Case 的问题

IRQ_MASK 是在cpsid i之后, sleep request之前写 1 的, 对于使用WFI的情况, 会存在 Corner Case 的问题

在整个suspend flow中如果发生中断, 都会被 KM0_IRQ_MASK 挡住, 要到PMC sleep时放开 KM0_IRQ_MASK 才能看到中断, 再触发wake的过程.对于KM4, 由于使用WFE, 所以不会有此corner case.

CG flow

CG suspend

CG resume

PG flow

PG suspend

PG resume

Deep Sleep Power Control Flow

Deep Sleep 唤醒的时候, 不需要有MASK控制, 只要将系统唤醒的IP记录到 AON_WAKE_EVET 即可, 如下左边方框中是AON domain的框图用于Deep Sleep唤醒, 右边是SYSON的框图用于Sleep Mode唤醒 (细节前面章节已经讲述) .

AON的几个IP比较特殊, AON_WAKE_PIN/ CHIP_EN/BOR 都是pulse触发事件, IP内部有Pulse2Level模块, 将LEVEL信号传给后面的NVIC/PMC模块.

AON IP wakeup flow

Aon Wake event 在software clear 对应中断status的时候被清除.

Power Mode

Deep Sleep

所有的SWR都被关电, 只有AON LDO和VD33有电.

SWR: HW自动关电, 无option 可以配置其在deepsleep下状态, wake的时候HW自动开电

Core LDO: HW自动关电, 无option 可以配置其在deepsleep下状态, wake的时候HW自动开电

LDO_1.8V: HW自动关电, wake的时候HW自动开电.

Aon LDO: 不关电, 默认在deepsleep下为0.7V , 如果需要在Deepsleep下维持0.8V, 需要software 修改AIP中0.7V对应code值, 使0.7V的configuration 使用0.8V的code.

Power Mode

Deep Sleep和如下两种mode存在转移关系, 所有状态转移都是由PMC完成的:

错误描述:下表中 1.7.1.3 章节不存在

Comment |

|

|---|---|

Snooze mode |

系统不会被唤醒, 只是某些电路醒过来一段时间之后再回到deep sleep mode, 详细信息请参考1.7.1.3 |

Active Mode |

系统被唤醒 |

Deep Sleep State Transition

Note

SDM有两种calibration, 其中always calibration不会发出 snooze request, 只有timer calibration会发出 snooze request, dslp的时候由于无法让PMC直接进入snooze mode, 需要SDM trigger才能进入snooze mode.此时不需要停掉 always calibration再启动timer calibration, 两种calibration保持常开即可.

Deepsleep mode中, SWR和Core LDO是联动的, SWR ON/OFF切换时LDO也会随之ON/OFF.SWR在snooze时工作在PFM mode,

Core_LDO工作在PC mode

Trigger Source |

Snooze |

Wakeup |

Comment |

|---|---|---|---|

SDM |

Y |

N |

|

RTC |

N |

Y |

1Hz |

AON Timer |

N |

Y |

100KHz |

AON GPIO |

N |

Y |

X2 |

BOR |

N |

Y |

|

SW_PDN |

N |

Y |

Power Control

Deep Sleep Power Control

Snooze Mode

只有SDM会将系统从Deep Sleep trigger到Snooze mode, AON PMC收到SDM的snooze request之后:

Step1: SDM发XTAL request给XTAL的Arbiter, 同时发送calibration request 给Aon PMC

Step2: AON PMC enable SWR core LDO 到0.8V PFM电压

Step3: 给SWR开电后, Aon PMC 使能

fen_lpon, 此时XTAL arb才开始工作, 同时自动会开 OSC4MStep4: SDM 看到XTAL valid 后会开始calibration

Step5: SDM calibration Done 以后会撤销request

Step6: DM req撤销后会让 XTAL arb 关掉 XTAL, 同时通知 aon pmc关 SWR (前者工作在4M, 速度快)

Step7:关掉SWR前会先把

fen_lpon拉低, 这个动作会把 OSC4M 关闭, 因为此时没有其他request了Step8:Aon PMC恢复到snooze mode前状态

Note

此时PAD可以保持和Deep Sleep一样的状态, 避免此时产生较高的漏电.

Power Domain

Power Domain |

Comment |

开关方式 |

|

|---|---|---|---|

AON |

PD_AON |

NA |

|

Regulator |

SWR |

周期性的被SDM唤醒(SNOOZE) SWR打开后, XTAL也会开电 |

Hardware |

Regulator |

LDO_Core |

与SWR 联动,工作在PC mode |

Hardware |

Regulator |

100K_OSC |

PMC需要这个clock |

NA |

Regulator |

128K_OSC |

RTC需要这个clock |

Software |

Regulator |

4M_OSC |

周期性的被SDM唤醒(SNOOZE) |

Hardware(关XTAL用) |

AON Power Domain

Deep Sleep Option

Active2Sleep |

|

|---|---|

100K |

|

AON LDO |

|

XTAL |

SDM request XTAL mode

|

SWR |

AON LDO/ SWR/Core LDO 在snooze mode 下联动电压 (同sleep共用配置) |

Sleep Mode

Power Control

Power Mode

Sleep State Transition

Trigger Source |

Sleep mode power change |

Wakeup |

Comment |

|---|---|---|---|

ADC Timer |

Y |

Y |

|

CTouch |

Y |

Y |

|

SDM |

Y |

N |

|

BT |

Y |

Y |

|

WIFI |

Y |

Y |

|

Other Wakeup Peripherals |

N |

Y |

|

Other Wakeup Peripherals 也包含ADC/CTouch/BT/WIFI |

Other Wakeup Peripherals 也包含ADC/CTouch/BT/WIFI |

Other Wakeup Peripherals 也包含ADC/CTouch/BT/WIFI |

Other Wakeup Peripherals 也包含ADC/CTouch/BT/WIFI |

Wake source

根据power 规划, 参考arch 中NVIC章节-- 此处引用无法确认参考章节的具体信息需补充

Power Domain

根据 Power Architecture, 从power domain看, 有Power switch的可以在sleep关电.

下面分章节详细讲述每个domain的应用场景.

ADC Timer/CTouch

ADC的clock source 可以来源于OSC4M 或者XTAL.

CLK source |

Restriction |

Note |

|---|---|---|

OSC 4M |

Core power在sleep下可以降到0.7V |

此case 要开osc4M, 因此会升压 |

XTAL 4M |

Core power在sleep下可以降到0.7V |

此case 要开XTAL, 因此会升压 |

SDM 32K Timer calibration

SDM |

SWR Request |

SWR Request |

XTAL Request |

XTAL Request |

|---|---|---|---|---|

SDM |

Voltage |

Mode |

Freq. |

Mode |

Calibration |

0.8 |

PFM |

40MHz |

NM/LPS |

Non Calibration |

0.7 |

PFM |

NA |

OFF |

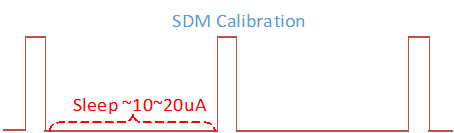

电流波形如下:

Step1: SDM发XTAL request给XTAL的Arbiter, 同时发送request 开OSC4M

Step2: OSC4M 会根据配置request SWR 电压 (至少

0.8V @PFM)Step3: 等待Core 电压稳定以后, OSC4M 开始工作, 此时XTAL Arbiter 开始工作,

Step4: XTAL Arbiter 打开 XTAL, SDM进行calibration

Step5: SDM calibration Done, XTAL request 消失, Arbiter会仲裁是否关闭XTAL

Step6: OSC4M enable Request也会消失, OSC4M也会仲裁是否关闭,

Step7: SWR Arbiter 也会因为OSC4M对于SWR的request 降低, 来调整SWR 电压

BT WoBT

如果不需要唤醒KM4, BT的运行应该独立于KM0, BT_PMC 负责给XTAL/SWR Arbiter发信号, 实现mode切换.下表是BT在不同mode下发给SWR/XTAL Arbiter的信号:

BT State |

SWR Request |

SWR Request |

XTAL Request |

XTAL Request |

OSC4M |

|---|---|---|---|---|---|

BT State |

Voltage |

Mode |

Freq. |

Mode |

Enable |

Active |

PWM |

40MHz 312.5K |

NM |

Y |

|

Sleep |

PFM |

312.5K |

LPS |

N |

Note

BT LPS起来恢复Rx状态的时候 (3081工作) , 此时CPU 不一定是Active的, 只有BT需要唤醒系统的时候才会给系统PMC发信号唤醒CPU.

在系统处于sleep mode时, SoC不request xtal时, BT使用312.5K作为32K来源时, 会request xtal lps, 此时只需要出来312.5K, 并不需要IDIG 40M输出.需要让designer 特别注意

BT处于sleep active mode时, 对于SWR 和CLK的request 需要做成software configurable

WIFI WoWLAN

WIFI PMC在不同mode下发给SWR/XTAL Arbiter的信号如下:

WIFI State |

SWR Request |

SWR Request |

XTAL Request |

XTAL Request |

|---|---|---|---|---|

WIFI State |

Voltage |

Mode |

Freq. |

Mode |

Active |

PWM |

40MHz |

HP |

|

Sleep |

PFM |

OFF |

Note

WIFI LPS起来恢复Rx状态的时候, 此时CPU 不一定是Active的, 只有WIFI需要唤醒系统的时候才会给系统PMC发信号唤醒CPU.

WIFI处于sleep active mode时, 对于SWR 和CLK的request 需要做成software configurable

电流波形如下:

KM0 PG and CG

整个系统进入sleep mode的时候, KM0有两种power save mode:

SOC |

Comment |

|

|---|---|---|

PG |

disable |

Sleep的时候SYSON PMC & WIFI PMC Arbiter后帮忙关闭SOC的Power |

CG |

enable |

1、Sleep的时候KM0将clock切至XTAL, 给PMC发sleep 信号, 并进入WFI 2、SYSON PMC给XTAL的Arbiter发close XTAL的信 |

Note

两种mode的选择, 主要考虑PG 时, backup 和 restore CPU 所浪费的时间间接提升了耗电, 这部分多耗掉的电是否可以由这一区的PG赚回来实测之后才能知道, 另外理论上CG会比PG更稳定.

Wake Source

XTAL |

SWR |

OSC4M |

OSC128K/SDM32K |

OSC100K |

|

|---|---|---|---|---|---|

UART |

PFM 0.8V |

XTAL LP 40MHz / OSC4M二选一 |

|||

CTouch |

ON |

ON |

|||

ADC |

ON |

||||

ADC comparator |

ON |

||||

WIFI |

PFM 0.7V |

ON |

|||

BT |

312.5K LP |

PFM 0.7V |

|||

LP Timer |

PFM 0.7V |

ON |

|||

PMC Timer |

PFM 0.7V |

||||

Keyscan |

PFM 0.7V |

||||

GPIO |

PFM 0.7V |

ON |

|||

RTC |

PFM 0.7V |

ON |

|||

AON_WAKEPIN |

PFM 0.7V |

ON |

|||

IWDG(WDG0) |

PFM 0.7V |

ON |

|||

VAD_BT |

40MHz LP |

PFM 0.7V |

|||

BOR |

PFM 0.7V |

||||

CHIP_EN |

PFM 0.7V |

Note

使用低速clock工作的peripheral唤醒时, 唤醒需要的clock不应该使用比这个IP工作更高的clock, 比如使用32K clock就可以工作的IP, 唤醒的clock不应该依赖于OSC4M.

对于唤醒有XTAL or OSC4M要求的wake source, 在系统sleep的时候不能降压到0.7V.因此Uart 唤醒, 需要维持XTAL

Sleep Option

除了 WAKE_MASK, 还有如下配置, 让PMC知道在sleep和wake的过程中怎样配置相应的function:

Active2Sleep |

Sleep2Active |

|

|---|---|---|

XTAL |

|

|

Power mode |

|

|

MEM |

|

|

OSC4M |

|

|

SOC_domain |

|

|

LDO_1.8V |

|

|

SWR XTAL Arbiter

系统Active的时候, XTAL与SWR 的Arbiter接收来自WIFI/BT/SDM等的request来自动切换SWR与XTAL的状态.

SWR Arbiter

Power mode

在Dplus的供电系统中, Core power 共有4种工作电压的组合, 分别为0.7V/0.8V/0.9V/1.0V.最终的工作电压和mode会有SWR arbiter 确定.

Core 电压由 SWR 和 LDO_CORE 共同确定, 全排列中会有2个bits的的电压值和1个bits的SWR mode值 2个bits Core LDO mode 值, 共会确定32种电压组合, 这些组合并非都是合理, 如下表格中的配置是实际应用场景中可能会使用, 硬件设计必须保证的

电压 |

0.7 V |

0.8V |

0.9V |

1.0V |

|---|---|---|---|---|

Aon LDO |

0.7V sleep |

0.8V sleep |

0.8V normal |

0.8V normal |

LDO core |

PC |

PC |

Sleep or Normal |

Sleep or Normal |

SWR |

PFM |

PFM |

PFM or PWM |

PFM or PWM |

0.7V / 0.8V 时, SWR 只能工作的PFM, 且此时Core LDO 工作在PC mode

Aon LDO的电压会随着core电压变化, 且Aon LDO的mode (sleep/normal) 由SYSON PMC根据OTP的状态确定, 在OTP power cut enable的时候工作在normal mode, 在power cut disable的时候工作在sleep mode

1.0V/0.9V 具有排他性, 也就是系统工作过程如果有1.0V就不会有0.9V, 有0.9V就不会有1.0V

Core LDO 在PC mode下, HW会自动remove dummy load

KM4 Active (非WFI or WFE时) HW会自动remove Core LDO的dummy load

Power calibration

Aon_LDO 有两档的电压值可以通过calibration 校准 (两组寄存器, software 可以配置) .Core LDO 有两档工作电压 (0.9V, 1.0V) , 工作电压值可以通过calibration 校准 (两组寄存器, software 可以配置) .SWR 有五档工作电压 (0.7V,0.8V,0.9V,1.25V,1.35V) , 但是因为PWM和PFM的电压code可能会不同.工作电压值共有 5 (PFM 5种) +3 (PWM仅支持1.35V,1.25V,0.9V) = 8 组寄存器可以配置可以通过calibration 校准 (八组寄存器, software 可以配置) ,

core电压 |

0.7 V |

0.8V |

0.9V |

1.0V |

|---|---|---|---|---|

Aon LDO |

0.7V 校准电压值 |

0.8V校准电压值 |

0.8V校准电压值 |

0.8V校准电压值 |

Core LDO |

PC mode |

PC mode |

0.9V校准电压值 |

1.0V校准电压值 |

SWR |

0.7V PFM校准电压值 |

0.8V PFM校准电压值 |

1.25V PFM/PWM校准值 |

1.35V PFM/PWM校准值 |

Arbiter status

系统regu状态组合如下, 绿色组合为目前可选配置组合

不同state的跳转需满足如下顺序关系

Arbiter Input

Arbiter的input 主要来源于如下4个component

WIFI

会在进入退出LPS时间点来切换request(5bits)

Request的configuration 可以在WIFI register中配置 (两组寄存器) , 默认MAC on时 request State 5.LPS时 request State 1

在Firmware 进入RX BCN后, 会配置 mac on 时 request State 4 (PFM). 在退出RX BCN 前会配置Mac on时 request State 5 (PWM)

WIFI mode |

request |

|

|---|---|---|

WIF PMC |

LPS/ OFF |

State 1 |

WIF PMC |

mac on(RX BCN) |

State 4 |

WIF PMC |

mac on(RX Normal/TX) |

State5 |

BT

会在进入退出LPS时间点来切换request

Request的configuration 可以在SYSON register中配置, 默认BT active时request State 5.Sleep时 request request State 1

BT 在系统进入sleep前, 需要根据32K来源来配置LPS时发出0.7V or 0.8V的request

SOC 在系统进入sleep前, 可以根据需要配置Mac on 后request的状态

BT mode |

request |

|

|---|---|---|

BT PMC |

LPS/ OFF |

SDM32K: State 1 Xtal32K: State 2 |

BT PMC |

mac on (包含TRX) |

State 5 |

PMC

会在KM4 wake ,gating 系统时时间点来切换request

Request的configuration, 可以在PMC register中配置, 默认KM4 active时 request State 6.系统 Sleep时 request State 1

SYS mode |

request |

|

|---|---|---|

SYS PMC |

KM0 sleep |

State 1 |

SYS PMC |

KM0 Active & KM4 Gating |

State 4 |

SYS PMC |

KM4 active |

State 6 |

OSC4M

会在有component 要enable 4M的时候 (例如SDM, Captouch, ADC) , 发出request.

OSC 发出的request 不可以配置, 在SOC4M off状态request state1 , 在ON的时候, request State2

总结各个source的default request 如下表, 所有的request 都是configurable的

Mode |

WIFI |

BT |

PMC |

OSC4M |

|---|---|---|---|---|

Active |

State 5 |

State 5 |

State 4 |

State 2 |

Sleep |

State 1 |

State 1 or State 2 |

State 1 |

State 1 |

High performance

系统仅在Boot(bootloader)时由efuse 决定boot core 电压(0.9V /1.0V)

System active的时候, Core 电压可以工作在0.9V, 也可以工作在1.0V.Boot 后不再做0.9V/1.0V切换.

ZCD控制

具体根据HW需求, 进行控制

Core Power

LDO_Core 共有3种工作mode, 三级dummy load, 其负载能力如下.

Mode |

MIN(A) |

MAX(A) |

|---|---|---|

PC |

— |

— |

Sleep |

2.00E-03 |

1.20E-01 |

Normal |

1.50E-02 |

3.50E-01 |

Dummy load |

Loading |

|---|---|

Level1 |

5.00E-03 |

Level2 |

1.00E-02 |

Level3 |

1.50E-02 |

SWR 共有PWM/PFM两种moe, 其负载能力如下

Mode |

最大负载能力 |

|---|---|

PWM 1.71->1.3125 |

4.00E-01 |

PWM 1.71->1.4175 |

3.00E-01 |

PWM 1.8->1.3125 |

5.00E-01 |

PWM 1.8->1.4175 |

4.00E-01 |

PWM others |

6.35E-01 |

PFM |

1.20E-01 |

Dummy Load

具体要求 参考HW spec(这里需给出参考源做引用), 为了方便配置, HW需要提供至少如下configuration

Config |

|

|---|---|

BT Sleep Dummy request |

|

BT Norm Dummy request |

|

WIFI Sleep Dummy request |

|

WIFI Norm Dummy request |

|

PMC Sleep Dummy request |

|

PMC Norm Dummy request |

|

Manual Dummy request |

|

Manual setting |

|

Dummy Load Level |

|

core LDO Dummy control

XTAL Arbiter

在Dplus中XTAL 共有3中工作mode.High performance, Normal以及LP mode. 其中需要特别注意的是LP mode 需要Core电压在0.8V及以上才能功能, 因此如果configuration XTAL 工作在LP mode , 系统至少要工作在0.8V PFM mode (调整PMC request 来保证)

Mode |

XTAL LP |

XTAL NORMAL |

XTAL HP |

|---|---|---|---|

Core power |

0.8V PFM or higher |

0.8V PFM or higher |

0.8V PFM or higher |

Note |

XTAL Core power 来源LDO Core |

XTAL Core power 来源Internal LDO |

XTAL Core power 来源Internal LDO |

Arbiter Input

Arbiter的input 主要来源于如下4个component

WIFI

在WIFI on的时候, 会request HP mode

在WIFI LPS的时候, 不会request XTAL

BT

在BT on的时候, 会request HP mode

在BT LPS的时候, 可能会request LP mode, 仅BT request xtal LPS时, 需要gating住40M 输出

PMC

在system active的时候, 会request Normal mode

在 sleep的时候会根据software configuration 来request Normal or LP or off

SDM

SDM Calibration时, 根据configuration 来request, 会是Normal or LP.

其他时间不进行request

总结各个source的request 如下表

Mode |

WIFI |

BT |

PMC |

OSC4M |

|---|---|---|---|---|

Active |

HP |

HP |

Normal (不可配置) |

Normal or LPS |

Sleep |

OFF |

LPS |

Normal or LPS or OFF |

OFF (不可配置) |

仅有 BT request xtal LPS时, 需要gating住40M 输出, 仅输出312.5K

OSC4M Arbiter

参考OSC4M design spec(需给出具体参考源以做引用)

Memory Control

Memory分布

Name |

Name |

Size |

Vendor |

Power Mode |

Control |

Power Domain |

|---|---|---|---|---|---|---|

HS_SRAM |

HS_SRAM |

512KB |

FTC_ULL_RW |

Active/LS/DS/SD |

SYSPMC |

PON |

Retention_RAM |

Retention_RAM |

512B |

FTC_ULL_RW |

Active/LS/DS/SD |

SYSPMC |

AON |

WIFI |

WLK4 |

40KB (16KB rxpktbuf + 24KB txpktbuf0) |

FTC_ULP |

Active/LS/DS/SD |

Wifi PMC / SYSPMC |

PON |

WIFI |

WPON |

8KB (txpktbuf1) |

FTC_ULL_RW |

Active/LS/DS/SD |

Wifi PMC |

WLON |

WIFI |

WPOFF |

11KB + 782B |

SNPS_ULP FTC_ULP |

Active/LS/DS/SD Active/LS |

Wifi PMC |

SOC |

BT |

BTONK4 |

56KB(btdmem) |

FTC_ULP |

Active/LS/DS/SD |

BT PMC / SYSPMC |

PON |

BT |

BTOFFK4 |

64KB(btbufram) |

FTC_ULP |

Active/LS/DS/SD |

BT PMC / SYSPMC |

PON |

CPU |

KM4 |

32KB (cache) |

FTC_ULP |

– |

SYSPMC |

SOC |

CPU |

KM4 |

288KB (ITCM ROM) |

FTC_ULP |

– |

SYSPMC |

SOC |

CPU |

KM0 |

32KB (cache) |

FTC_ULP |

– |

SYSPMC |

SOC |

CPU |

KM0 |

96KB (ITCM ROM) |

FTC_ULP |

– |

SYSPMC |

SOC |

PMC |

LSPMC_ROM |

576B |

FTC_ULL |

– |

– |

PON |

PMC |

AOKM0MC_ROM |

288B |

FTC_ULL |

– |

– |

AON |

Note

XXXXK4 表示可以和system share的memory

其中BT 部分和WIFI 部分可以单独控制Share

BT share 地址与HSRAM连续, WIFI share mem 地址紧随其后

Memory Power Mode Control

Memory 有些可以直接System去控制, 也有一些是BT/WIFI的PMC去控制的.AmebaDplus的memory的power Domain和主要控制的Master如下图:

Memory根据Vendor不同分为FTC, SKM4S, 他们对于memory的power mode control各不相同.

FTC《未更新》

由NDSP, RET, SLP这三个low power pin控制.

Power Mode |

NDSP(LS) |

RET(DS) |

SLP(SD) |

|---|---|---|---|

Active |

0 |

0 |

0 |

LS |

1 |

0 |

0 |

DS |

0 |

1 |

0 |

SD |

0 |

0 |

1 |

Note

还有CSB信号 (HW control)

对于RAM, CSB为0表示active

对于ROM, CSB为1表示active

RAM进退Low power mode的flow:

Enter lower power mode

set CSB to 1&gate mem clk, enter standby mode (for ROM, set CSB to0)set low power pin to

1after step a at least3T(请于clk停止之后再拉low power pin, 软件如何保证?)

Exit lower power mode

set low power pin to

0enable mem clk&set CSB to 0after step a at least 3T (for ROM, set CSB to1)

SKM4S《未更新》

由LS, DS, SD这三个low power pin控制.

Power Mode |

LS |

DS |

SD |

|---|---|---|---|

Active |

0 |

0 |

0 |

LS |

1 |

0 |

0 |

DS |

0 |

1 |

0 |

SD |

0 |

0 |

1 |

Note

ME信号的控制是HW自动实现

RAM进退Low power mode的flow:

Enter lower power mode

ME set 0&gate mem clkset low power pin to

1after step a at least 3T

Exit lower power mode

set low power pin to

0enable mem clk&set ME to 1after step a at least 3T

Note

SKM4S的LS/ARM的RETIN/ftc的NDSP是肯定都有的, 至于SKM4S的SD/DS ARM的RET2N/PGEN, FTC的RET/SLP有功能需求才会有.

Test chip因为内部design timing有问题, mem lower power mode除了SKM4S都是进不去的.ARM的DS, 当前只是验证过DS下mem不会丢失, 不确定有没有真正进入.

CPU Memory Control

CPU |

ROM/TCM |

Size |

Address |

BANK |

|---|---|---|---|---|

KM4 |

ITCM ROM |

288KB |

9 |

|

KM0 |

ITCM ROM |

96KB |

3 |

为了在CPU进低功耗mode时gate内部memory的clk以及在访问某块TCM时gate住其他BANK的clk, 增加下图的ICG (Integrated clock gating) 模块, 以降低CPU的power consumption.

改进电路分两部分:

上图右侧TCM内部的地址解析和ICG是在CPU active的时候gate住不用BANK的clk

左侧的ICG是当CPU主动进sleep mode时将总的clock gate住 (目前这部分实现会导致NVIC和systick等CPU module无法工作, 所以不增加)

Power save 状态下的控制

在system进入PG时, 对应SOC会power off , 对应Memory 也就没有电, 当系统进入CG的时候, 需要KM0 控制KM4 ITCM的状态, HW PMC 控制KM0 KM4 Cache ITCM 状态.

WIFI Memory Control

WIFI SRAM |

Size |

Vendor |

|---|---|---|

WLK4 |

40KB (24KB (txpktbuf0) + 16KB (rxpktbuf)) |

FTC_ULP |

WPON |

8KB |

FTC_ULP |

WPOFF |

11KB + 782B |

SKM0S_ULP / FTC_ULP |

WLK4是WIFI和system share的memory

WIFI ON: 该memory只可以被WIFI 使用.

WIFI OFF: 通过配置lpon register REG_PLAT_CTRL (

0x4100_8230) 的 bit18 为1, 开启system share WLK4 memory的功能.SW可以通过控制mem ctrl register来实时控制这块memory的power mode.如果不控制, 这块mem一直为active, 会产生额外的电流.

WPON和WPOFF是WIFI自己使用的mem, WLMAC其他memory SYS无法控制.WIFI OFF时memory没电, 此时mem ctrl register中的Power ctrl pin控制无效.

当WIFI Enable的时候, WIFI memory的power mode由WIFI PMC控制.当WIFI处于不同power mode (ON/OFF/LPS) 时, memory的power mode也会发生改变, WIFI的power mode由SW配置WIFI page0的register REG_WL_PMC_CTRL (

0x4000_0020) 的bit[2:0]实现切换WIFI ON mode ( BIT_WL_PMC_ONMAC (bit0) 控制): WIFI 所有的memory进入normal mode (active mode)

WIFI OFF mode ( BIT_WL_PMC_OFFMAC (bit1) 控制): 由于WPOFF memory 所在的power domain会被WIFI PMC关电, 所以WPOFF memory会掉电; WPON memory在PON区, 不会掉电

WIFI LPS mode ( BIT_WL_PMC_OFFMAC (bit2) 控制): WIFI memory的状态由WIFI page0的register REG_LPS_CTRL (

0x4000_0090) 控制Clock gate: BIT_WL_LPS_OPT_EMACPWR (REG_LPS_CTRL[8]) 和 BIT_WL_LPS_OPT_EMACFUN (REG_LPS_CTRL[10]) 都为

1Power gate: BIT_WL_LPS_OPT_EMACPWR (REG_LPS_CTRL[8]) 必须写

0, BIT_WL_LPS_OPT_EMACFUN (REG_LPS_CTRL[10]) 没有要求

WIFI SRAM |

WIFI SRAM power mode |

WIFI SRAM power mode |

WIFI SRAM power mode |

|---|---|---|---|

WIFI SRAM |

WIFI on |

WIFI off |

WIFI LPS |

WLK4 |

active |

SW可配 |

SW可配 (WIFI control) |

WPON |

active |

SW可配 (WIFI control) |

SW可配 (WIFI control) |

WPOFF |

active |

SD |

SW可配 (WIFI control) |

BT Memory Control

BT memory和system共享, System和BT PMC都可以控制这块mem的状态.

BT ON: 该memory只可以被BT 使用和控制.

BT OFF: 配置lpon register REG_PLAT_CTRL (

0x4100_c240) 的 bit19 为1, 开启system share BT memory的功能, SW即可以通过控制mem ctrl register来实时控制这块memory的power mode.如果不控制, 这块mem一直为active, 会产生额外的电流.

Retention Memory Control

Retention memory处于Aon 区域, 在sleep 和Dsleep都需要系统控制power 状态

Sleep: 有option 可以让software 配置retention Memory的状态, 默认是进入retention后处于retention状态

Deepsleep: 有option 可以让software 配置retention Memory的状态, 默认是进入retention后处于retention状态.

Top Level Interface

AON_PMC Interface

The AON_PMC interface is listed below.

Port Name |

I/O |

Description |

|---|---|---|

Global signals |

Global signals |

Global signals |

rst_n |

I |

Global reset signal, L active |

clk |

I |

Clock signal, 100KHz clk_ana |

eng_mode |

I |

Deleted Engineer mode, H active |

scan_mode |

I |

Scan mode signal, H active |

Register access interface |

Register access interface |

Register access interface |

outer_reg_ad[9:0] |

I |

Register address, unit in 4bytes |

outer_reg_wd[31:0] |

I |

Register write data |

outer_reg_wem[31:0] |

I |

Register maskable write enable |

outer_reg_we |

I |

Register write enable |

outer_reg_rdy |

O |

Register access ready |

OTP auto load interface |

OTP auto load interface |

OTP auto load interface |

load_done |

I |

Indicate AON domain auto load finish, H active |

load_fail |

I |

New added Indicate AON domain auto load fail, H active |

pmc_alden |

O |

PMC enable OTP do auto load of AON domain |

AON register interface |

AON register interface |

AON register interface |

r_PMC_PMEN_DSLP |

I |

Request AON PMC to deep sleep |

r_PMC_PMEN_NORM |

I |

Request AON PMC to normal(wake up event) |

r_PMC_PMEN_SNOOZE |

I |

Request AON PMC to snooze(snooze event) |

r_PMC_PMEN_RST |

I |

New added Reset from bor or thermal |

r_PMC_STL_SWR[1:0] |

I |

New added SWR power stable time 0: 64*T (T = 10us) 1: 128*T 2: 256*T 3: 512*T |

r_PMC_STL_BGP[1:0] |

I |

New added SWR bandgDSP stable time 0: 32*T (T = 10us) 1: 64*T 2: 128*T 3: 256*T |

r_PST_DSLP_EAOF |

I |

New added 1: AON_OFF domain power on when PMC enters deepsleep mode 0: AON_OFF domain power down when PMC enters deepsleep mode |

r_PST_DSLP_ERCK |

I |

1: Enable 100K clock for AON register access when PMC enters deepsleep mode 0: gated 100K clock |

r_PST_DSLP_LDHM |

I |

1: Eanble AON LDO into sleep mode when PMC enters deepsleep mode 0: Disable |

r_PMC_EN_SNOZ2NORM |

I |

Tied to 0 1: PMC exits snooze state immediately after receiving wakeup event 0: Upon receiving wakeup event, PMC switches to deepsleep from snooze firstly, then PMC exits from deepsleep state to normal |

r_PMC_SW_PDN_MODE |

I |

1: Software power down 0: Direct hardware power down |

r_PMC_SUPPORT_PDN |

I |

1: AON PMC supports power down 0: Not supported |

REGU Interface |

REGU Interface |

REGU Interface |

regu_chip_en |

I |

Deleted Indicate CHIP_EN status |

regu_LDO_COREpdn |

I |

Deleted |

regu_bod_reset_en |

I |

Deleted BOD reset Enable |

swr_bg_ok |

I |

SWR BandgDSP ready(New added) |

PMC state indication |

PMC state indication |

PMC state indication |

pmc_goto_pdn_eco |

O |

Deleted Output to CHIP_EN pad to notify HWPDN |

pmc_dslp_arckpd |

O |

Deleted Indicate AON 100KHz OSC is power down, H active |

pmc_snoz_mode |

O |

Indicate snooze mode |

pmc_exit_dslp_ps |

O |

Deleted Pulse to indicate deep sleep or snooze mode wake |

PMC ROM interface |

PMC ROM interface |

PMC ROM interface |

bist_mode_i |

I |

BIST mode signal, H active |

aoKM4mc_dout_i[17:0] |

I |

Data output from AON PMC ROM |

aoKM4mc_addr_o[5:0] |

O |

Address to AON PMC ROM |

aoKM4mc_cen_o |

O |

Address enable to AON PMC ROM |

aoKM4mc_clk_o |

O |

Clock to AON PMC ROM |

aoKM4mc_clken_o |

O |

Enable clock to AON PMC ROM |

PMC patch interface |

PMC patch interface |

PMC patch interface |

patch_hit |

I |

Indicate the current patch address is valid |

patch_code[17:0] |

I |

Patch code to replace ROM code |

patch_addr[5:0] |

O |

ROM Address need patch |

CTC interface(Deleted) |

CTC interface(Deleted) |

CTC interface(Deleted) |

adc_power_on |

O |

Indicate norm or snooze for CTC(Deleted) |

SDM interface |

SDM interface |

SDM interface |

XTAL_invalid |

I |

XTAL off indication iKM4ut |

Debug port |

Debug port |

Debug port |

dbg_o[31:0] |

O |

Debug port |

LS_SYSON_PMC Interface

ls_syson_pmc interface is shown below.

Port Name |

I/O |

Description |

|---|---|---|

Global signals |

Global signals |

Global signals |

rst_n |

I |

Global reset signal, L active |

clk |

I |

Clock signal, ANA 4MHz |

scan_mode |

I |

Scan mode signal, H active |

System Configuration |

System Configuration |

System Configuration |

pkg_eng_sel |

I |

Package for test |

tstmod_sel |

I |

Test mode with SIC function, H active |

Register access interface |

Register access interface |

Register access interface |

syson_reg_ad[8:0] |

I |

Register address, unit in 4bytes |

syson_reg_wd[31:0] |

I |

Register write data |

syson_reg_wem[31:0] |

I |

Register maskable write enable |

syson_reg_we |

I |

Register write enable |

syson_reg_rdy |

O |

Register access ready |

OTP auto load interface |

OTP auto load interface |

OTP auto load interface |

r_SYM_ALDN |

I |

System efuse register autoload done, H active |

pmc_alden |

PMC enable loader to do auto load |

|

load_done |

I |

Indicate auto load finish |

load_fail |

I |

Indicate auto load fail |

SYSON Register interface |

SYSON Register interface |

SYSON Register interface |

r_PMC_PMEN_NORM |

I |

Inform PMC enter normal mode, H active |

r_PMC_PMEN_SLEP |

I |

Inform PMC enter sleep mode, H active |

r_PMC_PMEN_DSLP |

I |

Inform PMC enter deep sleep mode, H active |

r_PMC_STL_PDSOC[1:0] |

I |

SOC powered stable time select |

r_PMC_STL_PDPBG[1:0] |

I |

KM4LL bandgDSP stable time select |

r_PMC_TUTIME |

I |

PMC time unit setting, in unit of ANA4M |

r_PMC_OPT_BKPOFIMK1 |

I |

Option 1 to enable break power off sequence by wake up event |

r_PMC_OPT_BKPOFIMK0 |

I |

Option 0 to enable break power off sequence by wake up event |

r_PST_NORM_FBUS |

I |

Normal setting for ls bus frequency selection 2’b00/01: ANA4M 2’b10: XTAL 2’b11: XTAL/2 |

r_PST_NORM_XMD |

I |

Normal setting for XTAL mode selection 00: XTAL will be off when PMC enter into normal mode 01: XTAL will be in LPS when PMC enter into normal mode 10/11: XTAL will be in Normal when PMC enter into normal mode |

r_PST_NORM_VOLT |

I |

Normal setting for SWR volt selection 00/01: SWR switch to 0.9v 10/11: SWR switch to 1.0v |

r_PST_NORM_EPWM |

I |

Normal setting for SWR mode selection 1: SWR switch to PWM mode when PMC enter normal mode 0: SWR switch to PFM when PMC enter normal mode |

r_PST_SLEP_FBUS |

I |

Sleep setting for ls bus frequency selection 2’b00/01: ANA4M 2’b10: XTAL 2’b11: XTAL/2 |

r_PST_SLEP_XMD |

I |

Sleep setting for XTAL mode selection 00: XTAL will be off when PMC enter into sleep mode 01: XTAL will be in LPS when PMC enter into sleep mode 10/11: XTAL will be in Normal when PMC enter into sleep mode |

r_PST_SLEP_VOLT |

I |

Sleep setting for SWR volt selection 00/01: SWR switch to 0.9v 10/11: SWR switch to 1.0v |

r_PST_SLEP_EPWM |

I |

1: SWR keeps at PWM mode when PMC enters into sleep mode 0: SWR switch to PFM when PMC enters into sleep mode |

r_PST_SLEP_ERCK |

I |

1: Enables LS SYSON register clock when PMC enters into sleep mode 0: Gate LS SYSON register clock when PMC enters into sleep mode |

r_PST_SLEP_EMPM |

I |

1: Memory power control setting don’t change when PMC enters into sleep mode 0: Memory power control settings change(0xD4[1]) when PMC enters into sleep mode |

r_PST_SLEP_EBUS |

I |

1: Enables platform clock when PMC enters into sleep mode 0: Gate platform clock when PMC enters into sleep mode |

r_PST_SLEP_EACK |

I |

1: Enables ANA4M CLK when PMC enters into sleep mode 0: Disables ANA4M CLK when PMC enters into sleep mode |

r_PST_SLEP_ESOC |

I |

1: Power enables SoC platform when PMC enters into sleep mode (clock-gate) 0: Power off SoC domain when PMC enters into sleep mode (power- gate) |

set_pst_lbus_clk |

O |

Setting lbus selection pulse |

set_pst_XTAL_mode |

O |

Setting XTAL mode pulse |

set_pst_swr_mode |

O |

Setting swr mode pulse |

set_pst_swr_volt |

O |

Setting swr voltage pulse |

set_pst_pad_mode |

O |

Setting pad mode pulse |

set_pst_lmem |

O |

Setting ls memory parameter |

set_pst_pll_on |

O |

Set pll enable pulse |

set_pst_pbg_on |

O |

Set pll bandgDSP enable pulse |

val_pst_lbus_clk[1:0] |

O |

Lbus source selection setting value |

val_pst_XTAL_mode[1:0] |

O |

XTAL mode setting value |

val_pst_swr_mode |

O |

swr mode setting value |

val_pst_swr_volt[1:0] |

O |

Swr volt setting value |

val_pst_pad_mode |

O |

Pad mode setting value |

val_pst_lmem |

O |

Ls memory mode setting value |

REGU Interface |

REGU Interface |

REGU Interface |

KM4ll_ckrdy |

I |

KM4LL ready |

volt_chg_ok |

I |

SWR volt change OK |

xmd_chg_ok |

I |

XTAL mode change OK |

sys_XTAL_mode_chg |

I |

“1” Indicate requesting XTAL mode different from current XTAL mode |

sys_swr_mode_chg |

I |

“1” Indicate requesting swr mode/volt different from current swr mode/volt |

PMC ROM interface |

PMC ROM interface |

PMC ROM interface |

bist_mode_i |

I |

BIST mode signal, H active |

syspmc_dout_i[17:0] |

I |

Data output from AON PMC ROM |

syspmc_addr_o[5:0] |

O |

Address to AON PMC ROM |

syspmc_cen_o |

O |

Address enable to AON PMC ROM |

syspmc_clk_o |

O |

Clock to AON PMC ROM |

syspmc_clken_o |

O |

Enable clock to AON PMC ROM |

PMC patch interface |

PMC patch interface |

PMC patch interface |

syspmc_pc_hit |

I |

Indicate the current patch address is valid |

syspmc_patch_instr[17:0] |

I |

Patch code to replace ROM code |

rw_pmc_patch_addr*[11:0] |

I |

PMC patch address |

syspmc_patch_addr[7:0] |

O |

ROM Address need patch |

PMC state indication |

PMC state indication |

PMC state indication |

snooze_mode |

I |

Snooze mode indication from aon_pmc, used to hold LS_SYSON PMC to PST_OFF state |

Debug interface |

Debug interface |

Debug interface |

dbg_en |

I |

Debug enable |

dbg_o[31:0] |

O |

Debug output |

pmc_tst_o[15:0] |

O |

PMC Test output |

Design implementation

Block diagram

AON PMC interface top

aon_pmc

rom code fetch and decode

power on sequence

deep sleep mode entry and wake up sequence

aon_pmc_rom

rom code for aon_pmc operations

aon_pmc_patch

patch code for error rom code.

ls_syson_pmc

rom code fetch and decode

power on sequence after SWR on

deep sleep/sleep mode entry and wake up sequence

ls_syson_pmc_rom

rom code for ls_syson_pmc operations

ls_syson_pmc_patch

patch code for error rom code.

AON_PMC

AON_PMC processes chip power on sequences when power on reset released. And it also processes the sequences when chip enters deep sleep mode.

AON_PMC State Machine

AON_PMC FSM state machine is shown below.

State Name |

Description |

|---|---|

PST_OFF |

Power off. When power on reset is not released, AON_PMC will stay PST_OFF. |

PST_NORM |

LS_SYSON domain’s power is ready and LS_SYSON function enabled. |

PST_DSLP |

CHIP is in deep sleep mode, SWR_09 is shut down. |

PST_SNOZ |

CHIP is in snooze mode (SWRC_09 is on) in order to do something, for example, calibration for SDM32K. But LS_SYSON function is disabled. |

PST_HRST |

HW reset, bor reset (low active) or thermal reset (low active) will trigger aon_pmc to PST_HRST |

AON_PMC FSM state machine transition is shown below.

From State |

To State |

Condition of transition |

|---|---|---|

PST_OFF |

PST_NORM |

After power on reset released, when AON_PMC’s power on sequence rom code has executed, AON_PMC jumps to PST_NORM. |

PST_NORM |

PST_HRST |

When r_PMC_PMEN_HRST is set, that is, bor reset (low active) or thermal reset (low active) hKM4pens. AON_PMC jumps to PST_HRST |

PST_NORM |

PST_DSLP |

After receives LS_SYSON_PMC’s request to deep sleep mode, when the deep sleep sequence rom code has executed, AON_PMC jumps to PST_DSLP. |

PST_DSLP |

PST_HRST |

When r_PMC_PMEN_HRST is set, that is, bor reset (low active) or thermal reset (low active) hKM4pens. AON_PMC jumps to PST_HRST |

PST_DSLP |

PST_NORM |

After receives a wake event from AON peripheral, when wake up sequence rom code has executed, AON_PMC jumps to PST_NORM. |

PST_DSLP |

PST_SNOZ |

If there’s no wake up event, and there’s snooze request from AON peripheral, when snooze sequence rom code has executed, AON_PMC jumps to PST_SNOZ. |

PST_SNOZ |

PST_HRST |

When r_PMC_PMEN_HRST is set, that is, bor reset (low active) or thermal reset (low active) hKM4pens. AON_PMC jumps to PST_HRST |

PST_SNOZ |

PST_DSLP |

When r_PMC_PMEN_SNOOZE is cleared and snooze request has done. Or when r_PMC_PMEN_SNOOZE is set and there’s a wake event and snooze request has done. |

PST_HRST |

PST_NORM |

When r_PMC_PMEN_HRST is released, AON_PMC jumps to PST_NORM. |

AON_PMC Power-on Sequence

AON_PMC power on flow (PST_OFF to PST_NORM)

LP PAD should be enabled after SWRC is enabled. AON pad reset and LP PAD reset only released once when power on.

SWR always in PWM mode

AON_PMC power on interface is shown below.

Port Name |

I/O |

Description |

|---|---|---|

VA33_AON |

A |

3.3V power supply |

VDD08_AON |

A |

AON LDO output supply for AON domain |

regu_pdn |

I |

CHIP_EN PAD |

POR_AON |

I |

Power on reset, L active |

CLK_OSC100K |

I |

100Khz clock from REGU |

clk_aon_gate |

I |

Register access clock for AON |

clk_aon |

I |

Register access clock for AON |

rr_prdy_swr |

I |

SWR power on ready |

AOKM4AD_RSTB33 |

O |

AON PAD (GPIOA) reset, only set once when power on |

AOKM4AD_SHDN33 |

O |

AON PAD (GPIOA) shutdown, only set once when power on |

rw_pow_sw |

O |

Power on SWR request |

LPPAD_RSTB33 |

O |

LP PAD (GPIOB/C/D) reset, only set once when power on |

LPPAD_SHDN33 |

O |

LP PAD (GPIOB/C/D) shutdown when in deepsleep |

iso_lp_syson_ram |

O |

LS domain isolation enable |

fen_lpon |

O |

LS domain function enable |

por_syson |

O |

LS domain reset, L active |

AON_PMC power on sequences diagram

AON_PMC Deepsleep Mode

AON_PMC deep sleep mode entry flow (PST_NORM to PST_DSLP)

When enter deepsleep, LP PAD only be disabled, should not be reset.

When enter deepsleep, have option to change AON LDO to sleep mode and disable CLK_AON_GATE

The flow of NORM2HRST and NORM2DSLP are consistent, except that NORM2HRST cannot change AON LDO to sleep mode and disable CLK_AON_GATE

AON_PMC power off interface is shown below.

Port Name |

I/O |

Description |

|---|---|---|

VA33_AON |

A |

3.3V power supply |

VDD08_AON |

A |

AON LDO output supply for AON domain |

regu_pdn |

I |

CHIP_EN PAD |

POR_AON |

I |

Power on reset, L active |

CLK_OSC100K |

I |

100Khz clock from REGU |

clk_aon_gate |

I |

Register access clock for AON |

rr_prdy_swr |

I |

SWR power on ready |

rw_pd_regu_1_1209 |

O |

1: power off core LDO |

core_ldo_dummy_en |

O |

1: enable dummy loading for core LDO |

rw_pow_sw |

O |

Power on SWR request |

rw_sys_pwm_req |

O |

1: switch SWR to PWM mode |

LPPAD_SHDN33 |

O |

LP PAD (GPIOB/C/D) shutdown when in deepsleep |

iso_lp_syson_ram |

O |

LS domain isolation enable |

fen_lpon |

O |

LS domain function enable |

rw_en_sleep |

O |

Set aon LDO to sleep mode, have option |

rw_cke_aon |

O |

Gated aon_clk, have option |

AON_PMC power off sequences diagram

AON_PMC deep sleep mode wake up flow (PST_DSLP to PST_NORM)

Enter PST_NORM from DSLP, will not to autoload from OTPC again

The flow of HRST2NORM as same as DSLP2NORM

AON_PMC Snooze Mode

AON_PMC snooze mode entry flow (PST_DSLP to PST_SNOZ)

When RTC needs work and support calibration in snooze mode,

Enter Snooze mode, no need to enable OTPC

AON_PMC snooze mode exit flow (PST_SNOZ to PST_DSLP)

LS_SYSON_PMC

LS_SYSON_PMC State Machine

LS_SYSON_PMC state machine

State Name |

Description |

|---|---|

PST_OFF |

Power off. When system reset (AON_PMC’s reset or BOR reset or POR reset or THM reset or WDG reset) is not released, or chip is in snooze mode, LS_SYSON_PMC will stay PST_OFF. |

PST_NORM |

LS system and LP/KM4 is ready to run. |

PST_SLEP |

CHIP is in sleep mode. |

PST_DSLP |

CHIP is in deep sleep mode(LS_SYSON_PMC part) |

AON_PMC FSM state machine transition is shown below.

From State |

To State |

Condition of transition |

|---|---|---|

PST_OFF |

PST_NORM |

After system reset released and if chip not in snooze mode, when LS_SYSON_PMC’s power on sequence rom code has executed, LS_SYSON_PMC jumps to PST_NORM. |

PST_NORM |

PST_SLEP |

After receives request to sleep mode, when the sleep sequence rom code has executed, LS_SYSON_PMC jumps to PST_SLEP. |

PST_SLEP |

PST_NORM |

After receives a wake event from chip peripherals, when wake up sequence rom code has executed, LS_SYSON_PMC jumps to PST_NORM. |

PST_NORM |

PST_DSLP |

After receives request to deep sleep mode, when the deep sleep sequence rom code has executed, LS_SYSON_PMC jumps to PST_DSLP. |

PST_DSLP |

PST_NORM |

After receives a wake event from chip peripherals, when wake up sequence rom code has executed, LS_SYSON_PMC jumps to PST_NORM. |

LS_SYSON_PMC Power-on Sequence

LS_SYSON_PMC power on flow (PST_OFF to `PST_NORM)

SWR’s power on voltage (0.9V or 1.25V) is decided by trKM4 or otp

LS_SYSON_PMC Sleep Mode

LS_SYSON_PMC sleep mode entry flow (PST_NORM to PST_SLEP)

When sleep, SWR have option to operate in PFM mode

When sleep, have option to disable plfm clock and gated OSC4M clock

When sleep, have option to disable HSOC

LS_SYSON_PMC sleep mode wake up flow (PST_SLEP to PST_NORM)

When waked from sleep mode, SWR switch from PFM to PWM mode

When waked from sleep mode, bypass autoload

When waked from sleep mode, enable KM0’s clock and function (KM4 or KM0)

LS_SYSON_PMC deep sleep mode

There are some differences between LS_SYSON_PMC deep sleep mode entry flow and sleep mode flow:

Deep sleep cannot disable platform clock

Deep sleep cannot gated system 4M clock

LS_SYSON_PMC sleep mode entry flow (PST_NORM to PST_DSLP)

When LS_SYSON_PMC enter deep sleep mode, will trigger AON_PMC enter DSLP, AON_PMC will reset LS_SYSON_PMC, wake up from DSLP, the state of LS_SYSON_PMC is changed from

PST_OFF -> PST_NORM.

PWC_SOC_ARB

Since wifi and hsoc will both use power cut of PD_SOC, when anyone of wifi or hsoc asserts a request of power on, soc_arb_pmc will start handling the process of power on. It will return a signal of grant to wifi and hsoc when completing the process.

request of powering on PD_SOC

Only if both wifi and hsoc assert a request of power off, soc_arb_pmc will start handling the process of power off. After asserts the request of power off, it’s no need to wait for a signal of grant from soc_arb_pmc and either of wifi and hsoc can continue with the following process of it’s own power off.

request of powering off PD_SOC

The figure shown below is state machine soc_arb_pmc .

The figure shown below is timing of power sequence of soc_arb_pmc. If both wifi and hsoc de-assert their requests, the pmc will start to trun off power cut of PD_SOC and react to new requests until the state machine is idle.