DSP ISS 仿真

使用指令集仿真器(Instruction Set Simulator ISS)进行程序分析(profile),可以帮助开发者在性能调优阶段快速定位性能瓶颈,从而优化算法架构。 ISS 仿真中的逻辑单元计算能力基本与真实芯片相同(如数据/代码均在缓存中的情况下,Cache 和 DTCM 的内存特性从配置中获取,可以确保此部分的准确性)。 在仿真环境下,系统内存只支持一种,因此 ISS 系统内存模型只能配置为 PSRAM 或 SRAM。 内存模型的差异会引入性能误差。根据不同程序特性,仿真误差一般在 10%以内,最大约为 20%。

Note

不支持多核心 IPC 通信,仅支持 DSP 内核算法仿真。

由于是精准指令仿真,仿真速度较慢,进行大型项目仿真时耗时较长。

建议使用 Xplorer 的 GUI 界面进行仿真。如果在 Linux 服务器上安装了 Xplorer,可以开启服务器的 X11 远程 GUI 进行使用。

编译工程

修改

<dsp sdk>\project\RTK_LSP\RI-2021.8\HIFI5_PROD_1123_asic_UPG\RTK_LSP\specs文件。*startfile: crt1-sim%O%s crti%O%s crtbegin%O%s _sharedvectors%O%s _vectors%O%s *endfile: crtend%O%s crtn%O%s *lib: -lc -lsim -lc -lhandler-reset -lhandlers-sim -lhal -lc

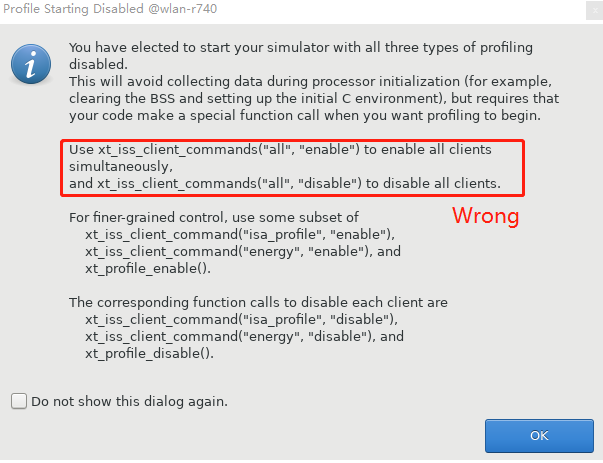

编辑代码并添加

exit()仿真退出函数,例如:#include <xtensa/sim.h> int main() { xt_iss_client_command("isa_profile", "enable"); xt_profile_enable(); // "Start with counting off" Option app_example(); // function for profile xt_profile_disable(); exit(1); }

重新编译工程。

配置和启动仿真

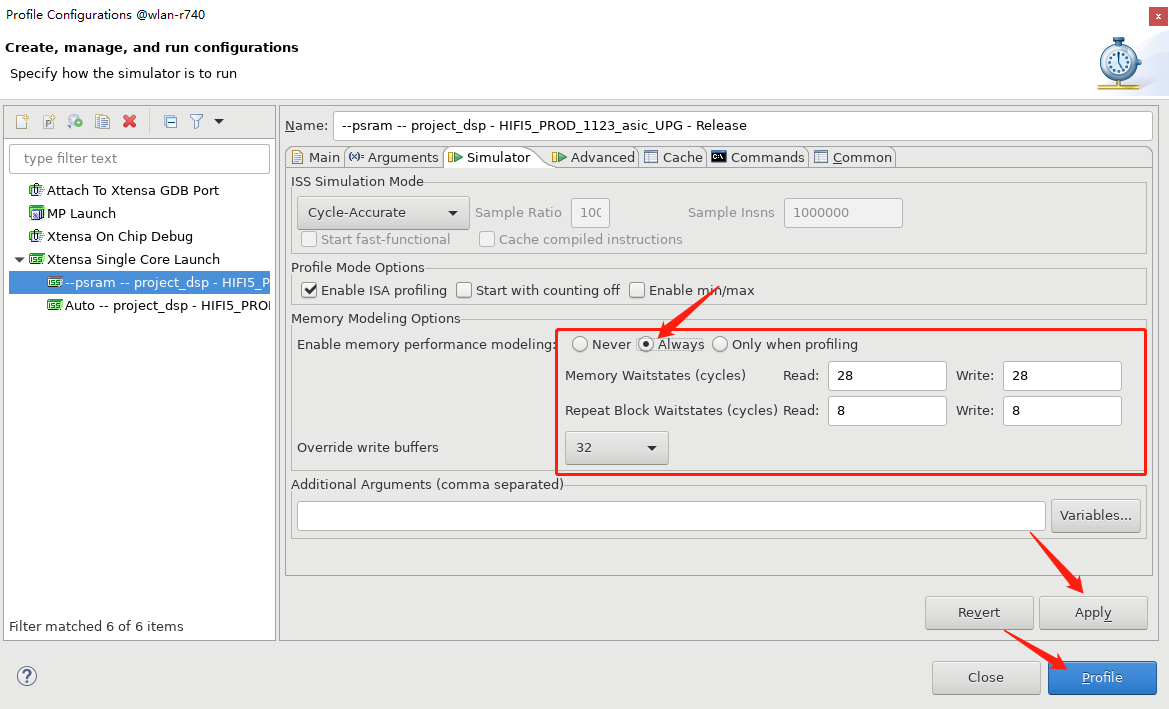

在工具栏点击 ,按需重命名仿真任务名称,并在 Profiling Mode Options 选项中勾选 Enable ISA profiling。

在 Memory Modeling Options 选项中修改 SRAM 和 PSRAM 的仿真参数(默认代码和数据是在 PSRAM 中):

项目

SRAM读取

SRAM写入

PSRAM读取

PSRAM写入

Memory Waitstates(cycles)

16

2

28

28

Repeat Block Waitstates(cycles)

2

2

8

8

点击 Apply 和 Profile 启动仿真。

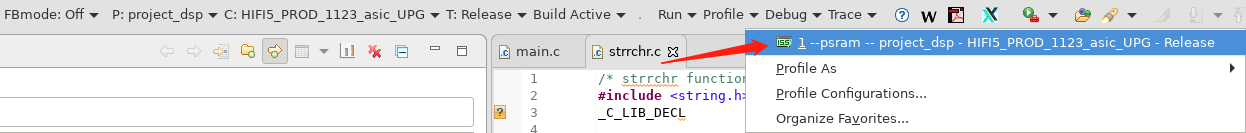

也可以点击下图中的设置按钮进行仿真。注意不能直接点击工具栏上的 profile 按钮,否则默认没有内存延迟模型。

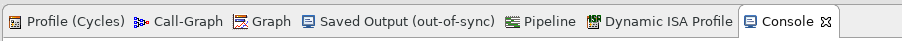

在仿真窗口的标签栏中有各种统计结果:

CMD 仿真

查看仿真指令

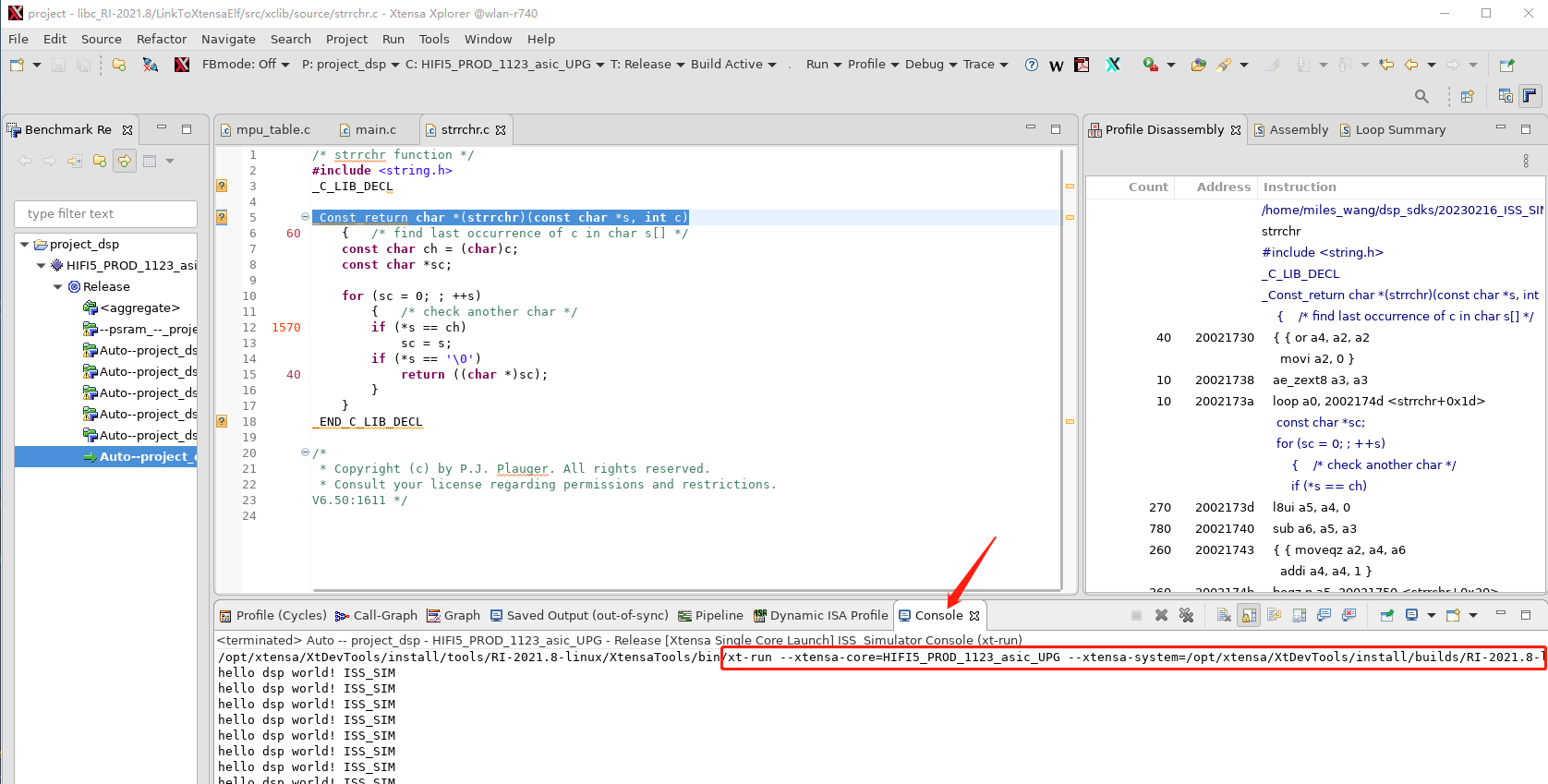

GUI 仿真完成后,可以点击下方的 Console 查看 Xplorer 仿真指令,例如:

/opt/xtensa/XtDevTools/install/tools/RI-2021.8-linux/XtensaTools/bin/xt-run --xtensa-core=HIFI5_PROD_1123_asic_UPG --xtensa-system=/opt/xtensa/XtDevTools/install/builds/RI-2021.8-linux/HIFI5_PROD_1123_asic_UPG/config --xtensa-params= --console --mem_model --wbsize=32 --mlatency=28 --blockrepeat=8 --write_delay=28 --write_repeat=8 --summary --client=<dsp sdk>/project/project_dsp/bin/HIFI5_PROD_1123_asic_UPG/Release/_gen_d/profile/--psram_--_project_dsp_-_HIFI5_PROD_1123_asic_UPG_-_Release/p_10/iss.clientcmds --vector=1 --alt_reset_vec=0x60301000 <dsp sdk>/project/project_dsp/bin/HIFI5_PROD_1123_asic_UPG/Release/project_dsp

修改指令

用户需要根据实际项目配置及文件路径进行调整。如果在 Linux 下使用

auto_build.sh脚本编译 project_dsp,需要根据实际情况修改 xt-run 命令。 例如,auto_build.sh会将项目拷贝到<dsp sdk>/auto_ws目录再编译,那么 CMD 最后参数(/home/miles_wang/dsp_sdks/20230216_ISS_SIM/dsp/project/project_dsp/bin/HIFI5_PROD_1123_asic_UPG/Release/project_dsp)就需据实际情况修改到 ELF 文件所在位置。运行指令

在终端中正常运行上面的命令即可。

Profile 与 FreeRTOS Task 问题

当前,Xplorer 提供的 profile 方法对于异常和中断函数调用的处理还不完善,一般算法调优也可以独立于 FreeRTOS 系统进行。因此,我们强烈不推荐在 FreeRTOS 系统下进行 profile。

如果用户必须在 FreeRTOS Task 环境里 profile:

profile 时防止上下文切换和处理中断服务。

进入统计区域前完成一次 lazy switch。因为 FreeRTOS 的任务切换不会改变协处理器寄存器,仅当任务用到这些 DSP 寄存器时,才会生成协处理器寄存器异常。

例如:

void profiling_task(void)

{

int start, end;

vTaskEnterCritical();

co_processor_func(test_array); // this function uses DSP co-processor registers start = xthal_get_ccount();

xt_iss_client_command("isa_profile", "enable");

xt_profile_enable();

for (int i = 0; i < 1000; ++i) {

co_processor_func (test_array);

}

xt_profile_disable ();

end = xthal_get_ccount();

vTaskExitCritical();

printf("%d cycles\n", end-start); // output: 314313 cycles

exit(1);

}

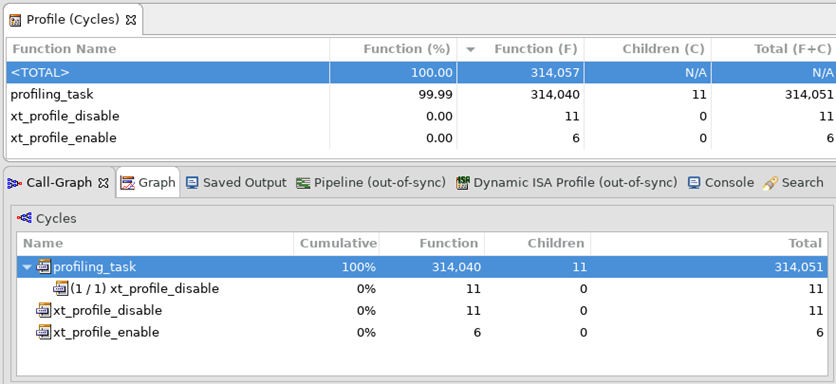

Profile 结果如下:

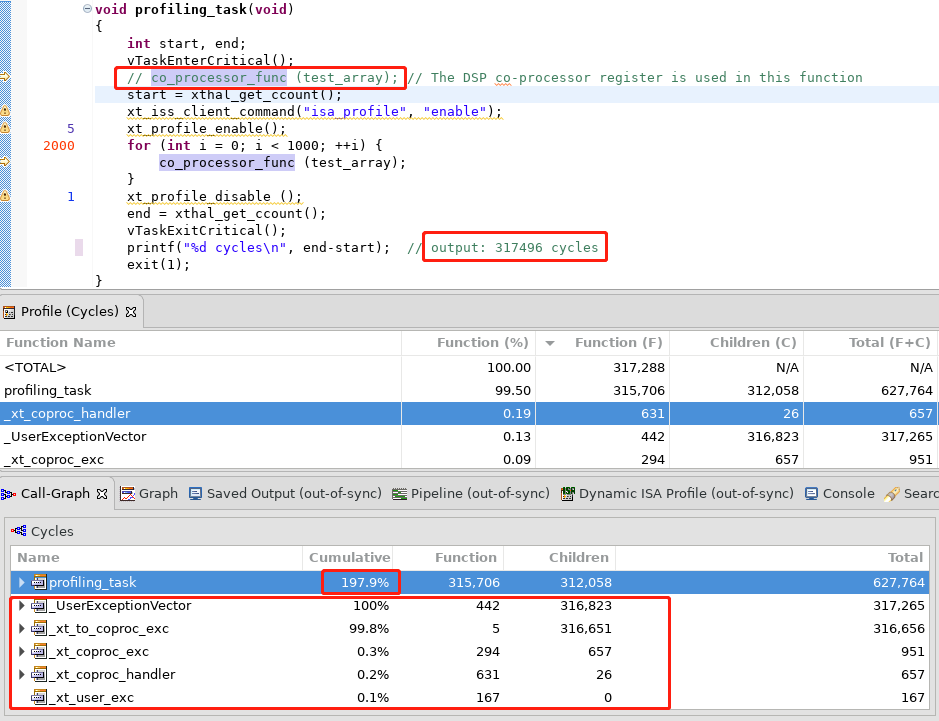

如果取消第一次 co_processor_func() 的调用,则会发现出现了部分异常 handler,Xplorer 对这些 handler 的统计会出错: Profile (Cycles) 表统计正确,但 Call-Graph 表会出现统计错误。

参考文档

具体 ISS 仿真方法和 profile 结果分析,请参考 Xtensa 文档。