Introduction

The chip supports Motorola Serial Peripheral Interface (SPI) – A four-wire, full-duplex serial protocol.

Features

Supports Motorola SPI Serial interface operation

Master or slave operation mode

Provides two high-speed SPI ports: configured as master or slave with max. baud rate 50Mbps

DMA interface for DMA transfer

Independent masking of interrupts

The Transmit and Receive FIFO buffers are 64 words depth. The FIFO width is fixed at 16 bits.

Hardware/Software slave-select

Dedicated hardware slave-select lines

Software control to select target the serial-slave device

Programmable features

Clock bit-rate – Dynamic control of the serial bit rate of the data transfer; only when configured in master mode

Data frame size (4 to 16 bits) – Frame size of each data transfer under the control of the programmer.

Configurable clock polarity and phase

Programmable delay on the sample time of the received serial data bit (rxd), when configured in master mode

Transfer mode

Transmit and receive

Transmit only

Receive only

Operation mode

Polling mode

Interrupt mode

DMA mode

Block Diagram

The following figure shows the following functional groupings of the main interfaces to the SPI block.

APB Interface: A bus interface for low bandwidth control access. The processor accesses data, control, and status information on the SPI device through this APB interface.

Register Block: Contains configuration registers and is the interface with software.

DMA Interface: Generates the handshaking signals to the central DMA controller in order to automatically transfer the data without CPU intervention. The hardware handshake interface acts an important role in controlling data flow so that data overflow and underflow can be avoided.

Transmit FIFO Control/Receive FIFO Control: Records the level of the FIFO.

Transmit FIFO Memory/Receive FIFO Memory: Stores data in the FIFO or removes data out of the FIFO. The depth of each FIFO is 64 bytes.

FSM Control: Controls the state change of the SPI device.

Shift Control Logic: Shifts out data out of the FIFO bit by bit.

Interrupt Logic: Generates the raw interrupt and interrupt flags, allowing them to be set and to be cleared.

Clock Pre-scale: Generates clk from pclk. The sclk is configurable by setting the BAUDR register.

Functional Description

This section describes the functional operation of the SPI.

The SPI is a configurable, synthesizable, and programmable component that is a full-duplex master or slave-synchronous serial interface. It can be configured in one of two modes of operations: as a serial master or a serial slave. The SPI can connect to any serial-master or serial-slave peripheral device using Motorola Serial Peripheral Interface (SPI).

Introduction

In order to connect to a serial-master or serial-slave peripheral device for the SPI, the peripheral must have Motorola Serial Peripheral Interface (SPI) – A four-wire, full-duplex serial protocol from Motorola.

The serial protocols supported by the SPI allow for serial slaves to be selected or addressed.

Single slave: connecting master's Slave Select pin to slave's Slave Select pin.

Multiple slaves: As the SPI master has only a single slave select output (determined by SPI hardware design), users should use GPIOs to control multiple SPI salves. Only one slave should be selected at any time.

Motorola Serial Peripheral Interface (SPI)

There are four possible combinations for the serial clock phase and clock polarity. The clock phase (SCPH) determines whether the serial transfer begins with the falling edge of the slave select signal or the first edge of the serial clock. The clock polarity (SCPOL) configuration parameter determines whether the inactive state of the serial clock is high or low. To transmit data, both SPI peripherals must have identical serial clock phase (SCPH) and clock polarity (SCPOL) values.

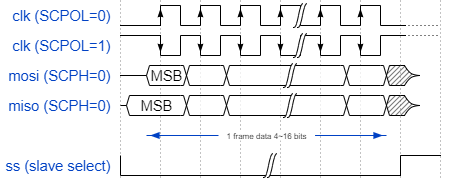

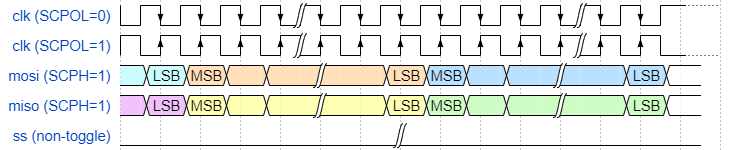

When the configuration parameter SCPH = 0, data transmission begins on the falling edge of the slave select signal. The first data bit is captured by the master and slave peripherals on the first edge of the serial clock; therefore, valid data must be present on the MOSI and MISO lines prior to the first serial clock edge. The following figure shows a timing diagram for a single SPI data transfer with SCPH = 0. The serial clock is shown for configuration parameters SCPOL = 0 and SCPOL = 1.

The signals are illustrated in the timing diagrams.

SPI serial format (SCPH = 0)

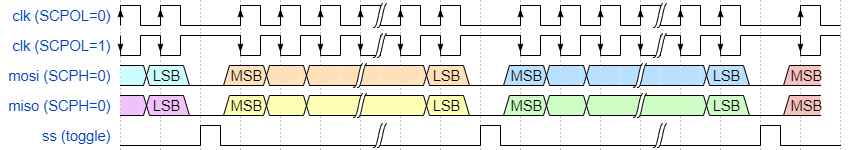

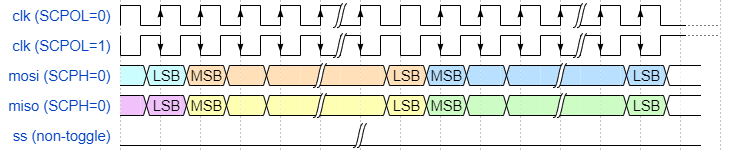

As data transmission starts on the falling edge of the slave select signal when SCPH = 0, whether the slave select signal of SPI master should toggle or not before the next data frame during continuous data transfer can be configured through SS_T in CTRLR0 register. The SPI slave can communicate with serial-master no matter that the slave select signal from master is toggling or not during continuous data transfer. The timing diagram of SS toggling is illustrated and the timing diagram of SS not-toggling is illustrated below. SS toggling function is used to compatible with different SPI devices.

SPI serial format continuous transfers (SCPH = 0 and SS toggling)

SPI serial format continuous transfers (SCPH = 0 and SS not-toggling)

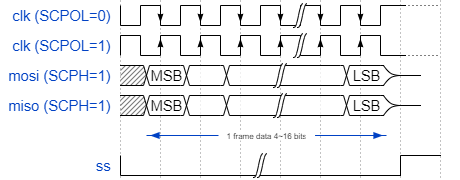

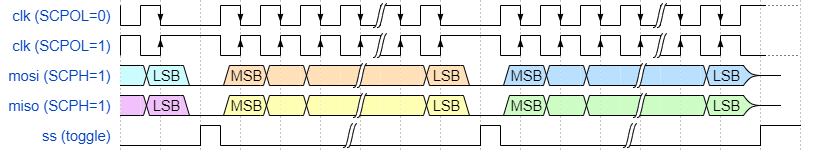

When the configuration parameter SCPH = 1, both master and slave peripherals begin transmitting data on the first serial clock edge after the slave select line is activated. The first data bit is captured on the second (trailing) serial clock edge. Data are propagated by the master and slave peripherals on the leading edge of the serial clock. During continuous data frame transfers, the slave select line may be held active-low until the last bit of the last frame has been captured. The following figure shows the timing diagram for the SPI format when the configuration parameter SCPH = 1.

SPI serial format (SCPH = 1)

Continuous data frames are transferred in the same way as single frames, with the MSB of the next frame following directly after the LSB of the current frame. The slave select signal is held active for the duration of the transfer. The following figure shows the timing diagram for continuous SPI transfers when the configuration parameter SCPH = 1.

SPI serial format continuous transfers (SCPH = 1 and SS not toggling)

SPI serial format continuous transfers (SCPH = 1 and SS toggling)

Clock Ratios

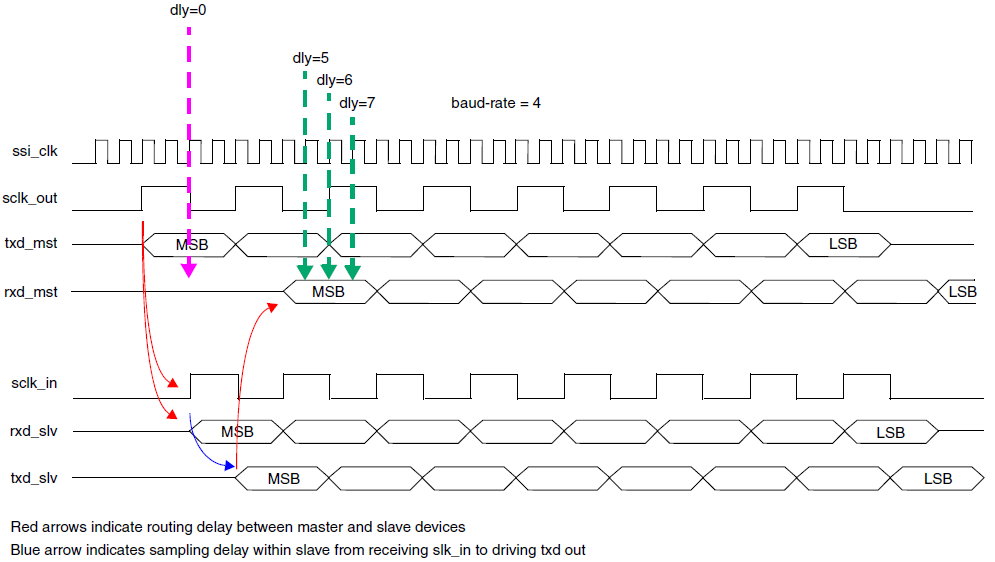

When SPI is configured as a master device, the maximum frequency of the bit-rate clock (sclk_out) is one-half the frequency of ssi_clk. This allows the shift control logic to capture data on one clock edge of sclk_out, and propagate data on the opposite edge; as illustrated below. The sclk_out line toggles only when an active transfer is in progress. At all other times, it is held in an inactive state, as defined by the serial protocol under which it operates.

The frequency of sclk_out can be derived from the following equation:

Fsclk_out= Fssi_clk/SCKDV

SCKDV is a bit field in the programmable register BAUDR, holding any even value in the range 0 to 65,534. If SCKDV is 0, then sclk_out is disabled.

Maximum sclk_out/ssi_clk Ratio

The chip supports high-speed SPI slave. When SPI is configured as a slave device, the maximum frequency of the bit-rate clock (sclk_in) provided by serial master can reach up to one-half the frequency of ssi_clk.

A summary of the frequency ratio restrictions between bit-rate clock (sclk_out/sclk_in) and SPI peripheral clock (ssi_clk) are described as:

Master: Fssi_clk >= 2 × (maximum Fsclk_out)

Slave: Fssi_clk >= 2 × (maximum Fsclk_out)

The Fssi_clk of SPI0 is 100MHz, the same as the Fssi_clk of SPI1.

Transmit and Receive FIFO Buffers

The depth of both transmit and receive FIFO buffers is 64. The width is fixed at 16 bits due to the serial specifications, which state that a serial transfer (data frame) can be 4 to 16 bits in length. Each data entry in the FIFO buffers contains a single data frame.

Note

The transmit and receive FIFO buffers are cleared when the SPI is disabled (SSI_EN = 0) or when it is reset.

The transmit FIFO is loaded by APB write commands to the SPI data register (DR). Data are popped (removed) from the transmit FIFO by the shift control logic into the transmit shift register. The transmit FIFO generates a FIFO empty interrupt request (ssi_txe_intr) when the number of entries in the FIFO is less than or equal to the FIFO threshold value. The threshold value, set through the programmable register TXFTLR, determines the level of FIFO entries at which an interrupt is generated. The threshold value allows you to provide early indication to the processor that the transmit FIFO is nearly empty. A transmit FIFO overflow interrupt (ssi_txo_intr) is generated if you attempt to write data into an already full transmit FIFO.

Data are popped from the receive FIFO by APB read commands to the SPI data register (DR). The receive FIFO is loaded from the receive shift register by the shift control logic. The receive FIFO generates a FIFO-full interrupt request (ssi_rxf_intr) when the number of entries in the FIFO is greater than or equal to the FIFO threshold value plus 1. The threshold value, set through programmable register RXFTLR, determines the level of FIFO entries at which an interrupt is generated.

The threshold value allows you to provide early indication to the processor that the receive FIFO is nearly full. A receive FIFO overrun interrupt (ssi_rxo_intr) is generated when the receive shift logic attempts to load data into a completely full receive FIFO. However, this newly received data are lost. A receive FIFO underflow interrupt (ssi_rxu_intr) is generated if you attempt to read from an empty receive FIFO. This alerts the processor that the read data are invalid.

SPI Interrupts

The SPI supports combined and individual interrupt requests, each of which can be masked. The combined interrupt request is the ored result of all other SPI interrupts after masking. The system designer has the choice of routing individual interrupt requests or only the combined interrupt request to the Interrupt Controller. The SPI interrupts are described as follows:

Transmit FIFO Empty Interrupt (

ssi_txe_intr) – Set when the transmit FIFO is equal to or below its threshold value and requires service to prevent an under-run. The threshold value, set through a software-programmable register, determines the level of transmit FIFO entries at which an interrupt is generated. This interrupt is cleared by hardware when data are written into the transmit FIFO buffer, bringing it over the threshold level.Transmit FIFO Overflow Interrupt (

ssi_txo_intr) – Set when an APB access attempts to write into the transmit FIFO after it has been completely filled. When set, data written from the APB is discarded. This interrupt remains set until you read the transmit FIFO overflow interrupt clear register (TXOICR).Receive FIFO Underflow Interrupt (

ssi_rxu_intr) – Set when an APB access attempts to read from the receive FIFO when it is empty. When set, zeros are read back from the receive FIFO. This interrupt remains set until you read the receive FIFO underflow interrupt clear register (RXUICR).Receive FIFO Overflow Interrupt (

ssi_rxo_intr) – Set when the receive logic attempts to place data into the receive FIFO after it has been completely filled. When set, the newly received data are discarded. This interrupt remains set until you read the receive FIFO overflow interrupt clear register (RXOICR).Receive FIFO Full Interrupt (

ssi_rxf_intr) – Set when the receive FIFO is equal to or above its threshold value plus 1 and requires service to prevent an overflow. The threshold value, set through a software-programmable register, determines the level of receive FIFO entries at which an interrupt is generated. This interrupt is cleared by hardware when data are read from the receive FIFO buffer, bringing it below the threshold level.Frame Alignment Error Interrupt (

ssi_fae_intr) – Present only if the SPI is configured as a serial-slave device. The interrupt is set when the received data frame length is not matching the DFS (Data Frame Size) setting in CTRLR0. This interrupt remains set until you read the Frame Alignment Error Interrupt Clear Register (MSTICR_FAEICR).Multi-Master Contention Interrupt (

ssi_mst_intr) – Unable to use on this chip.Transmit FIFO under Flow Interrupt (

ssi_txu_intr) – Present only if the SPI is configured as a serial-slave device. The interrupt is set when transmit logic attempts to read from transmit FIFO when it is empty. When set, data sent from slave device is invalid. This interrupt remains set until you read the transmit FIFO underflow interrupt clear register (TXUICR).SS_N Rising Edge Detect Interrupt (

ssi_ssr_intr) – Present only if the SPI is configured as a serial-slave device. The interrupt is set when SS_N Rising Edge is detected. This interrupt remains set until you read the SS_N Rising Edge Detect Interrupt Clear Register (SSRICR).

SPI Master/Slave Role Set

There are two different sets of circuits when the chip works as SPI Master or SPI Slave, so users need to set the SPI role before initializing the device, the relevant register is described below.

Name: REG_LSYS_PLAT_CTRL

Size: 32 bits

Base Address:

0x4100C000Address offset:

0x230Read/write access: read/write

This register is valid only when the SPI is configured as serial-master.

Bit |

Name |

Access |

Reset |

Description |

|---|---|---|---|---|

27 |

SPI1_MST |

R/W |

0x0 |

|

26 |

SPI0_MST |

R/W |

0x0 |

|

Transfer Modes

When transferring data on the serial bus, the SPI master can operate in transmit and receive mode, transmit only mode or receive only mode as following. The transfer mode (TMOD) is set by writing to control register 0 (CTRLR0).

When transferring data on the serial bus, the SPI slave can only operate in transmit and receive mode. That is, TMOD field in CTRLR0 register is invalid for SPI slave. If you do not want this device to respond with data, slave output can be disabled through SLV_OE bit in CTRLR0.

Transmit and Receive

When TMOD = 2'b00, both transmit and receive logic are valid. Transmit data are popped from the transmit FIFO and sent through the MOSI line to the target device, which replies with data on the MISO line. The received data from the target device is moved from the receive shift register into the receive FIFO at the end of each data frame.

Transmit Only

When TMOD = 2'b01, the receive data are invalid and should not be stored in the receive FIFO. Transmit data are popped from the transmit FIFO and sent through the MOSI line to the target device, which replies with data on the MISO line. At the end of the data frame, the receive shift register does not load its newly received data into the receive FIFO. The data in the receive shift register is overwritten by the next transfer. You should mask interrupts originating from the receive logic when this mode is entered.

Receive Only

When TMOD = 2'b10, the transmit data are invalid. The MOSI output remains at a constant logic level during the transmission. The received data from the target device is moved from the receive shift register into the receive FIFO at the end of each data frame. You should mask interrupts originating from the transmit logic when this mode is entered.

Operation Modes

The SPI can be configured in the fundamental modes of operation discussed in this section.

Serial-Master Mode

This mode enables serial communication with serial-slave peripheral devices by software. When configured as a serial-master device, the SPI initiates and controls all serial transfers. This figure shows an example of the SPI configured as a serial master with all other devices on the serial bus controlled by GPIO as slave select signal.

The serial bit-rate clock, generated and controlled by the SPI master, is driven out on the sclk_out line. When the SPI is disabled (SSI_EN = 0), no serial transfers can occur and sclk_out is held in an inactive state.

RXD Sample Delay

The slave uses the clk signal from the master as a strobe in order to drive MOSI/MISO signal data onto the serial bus. As there are round trip routing delays on clk signal from master, slave drive data output may delay at the same time as seen by the master, which has moved away from the normal sampling time. When the SPI is configured as a master, additional logic can be included in the design in order to delay the default sample time of the MISO signal. This additional logic can help to increase the maximum achievable frequency on the serial bus.

The following figure shows an example of how a routing delay on the MOSI signal can result in an incorrect MISO value at the default time when the master samples the port. Where, blue arrows indicate routing delay between master and slave devices; red line indicates sampling delay within slave from receiving clk to drive data out on MISO line.

Effects of round trip routing delays on clk signal

When the RXD Sample Delay logic is included, user can dynamically program a delay value in order to move the sampling time of the rxd signal equal to a number of pclk cycles from the default.

The sample delay logic has a resolution of one pclk cycle. Software can “train” the serial bus by coding a loop that continually reads from the slave and increments the master's RXD Sample Delay value until the correct data is received by the master.

Note

The maximum number of ssi_clk cycles that can be used to delay the sampling of the rxd input is 4. If programmed delay value exceeds the maximum number, a zero (0) delay will be applied to the rxd sample.

Data Transfers

Data transfers are started by the serial-master device. When the SPI is enabled (SSI_EN=1), at least one valid data entry is present in the transmit FIFO and a serial-slave device is selected. When actively transferring data, the busy flag (BUSY) in the status register (SR) is set. You must wait until the busy flag is cleared before attempting a new serial transfer.

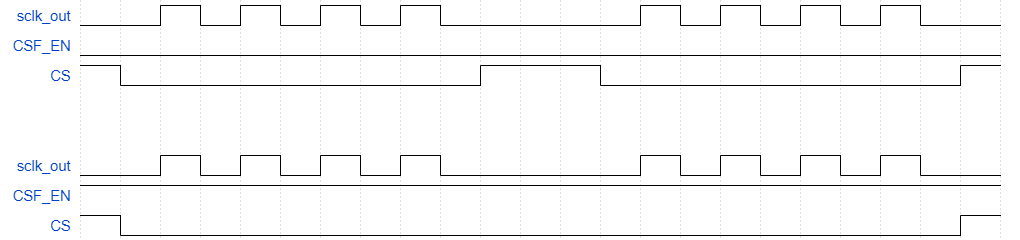

CS Force Control

Not support.

Not support.

Not support.

Not support.

Not support.

For some of the situations, interrupts might not service in time to fill the TX FIFO to make sure it's not empty. Hence, CSF_EN bit in register CTRLR0 allows SPI master to force CS signal to keep low until the whole transmission is complete. Moreover, SPI master will keep the CS signal low and pause the transmission (not sending sclk out) when the TX FIFO is empty during the transmission is not yet complete.

When the CSF_EN bit is enabled, the SPI master will calculate the number of data bits that will be sent. This is done by multiplying the Data Frame Size (CTRLR0 [3:0]) by the Number of Data Frames (CTRLR1 [15:0]). After that, SPI master will force the CS signal low during transmission. The SPI master will only release the force when the data has been sent is reach the calculated amount of data bits. The example use of CSF_EN is illustrated below.

Master SPI Serial Transfers

When the transfer mode is “transmit and receive” or “transmit only” (TMOD = 2'b00 or TMOD = 2'b01, respectively), transfers are terminated by the shift control logic when the transmit FIFO is empty. For continuous data transfers, you must ensure that the transmit FIFO buffer does not become empty before all the data have been transmitted. The transmit FIFO threshold level (TXFTLR) can be used to early interrupt (ssi_txe_intr) the processor indicating that the transmit FIFO buffer is nearly empty.

When a DMA is used for APB accesses, the transmit data level (DMATDLR) can be used to early request (dma_tx_req) the DMA Controller, indicating that the transmit FIFO is nearly empty. The FIFO can then be refilled with data to continue the serial transfer. The user may also write a block of data (at least two FIFO entries) into the transmit FIFO before enabling a serial slave. This ensures that serial transmission does not begin until the number of data-frames that make up the continuous transfer are present in the transmit FIFO.

When the transfer mode is “receive only” (TMOD = 2'b10), a serial transfer is started by writing one “dummy” data word into the transmit FIFO when a serial slave is selected. The MOSI output from the SPI is held at a constant logic level for the duration of the serial transfer. The transmit FIFO is popped only once at the beginning and may remain empty for the duration of the serial transfer. The end of the serial transfer is controlled by the ‘number of data frames’ (NDF) field in control register 1 (CTRLR1).

If, for example, you want to receive 24 data frames from a serial-slave peripheral, you should program the NDF field with the value 23; the receive logic terminates the serial transfer when the number of frames received is equal to the NDF value + 1. This transfer mode increases the bandwidth of the APB bus as the transmit FIFO never needs to be serviced during the transfer. The receive FIFO buffer should be read each time the receive FIFO generates a FIFO full interrupt request to prevent an overflow.

The receive FIFO threshold level (RXFTLR) can be used to give early indication that the receive FIFO is nearly full. When a DMA is used for APB accesses, the received data level (DMARDLR) can be used to early request (dma_rx_req) the DMA Controller, indicating that the receive FIFO is nearly full.

A typical software flow for completing an SPI serial transfer from the SPI serial master is outlined as follows:

If the SPI is enabled, disable it by writing 0 to the SSI Enable register (SSIENR).

Set up the SPI control registers for the transfer; these registers can be set in any order.

Write Control Register 0 (CTRLR0). For SPI transfers, the serial clock polarity and serial clock phase parameters must be set identical to target slave device.

If the transfer mode is receive-only, write Control Register 1 (CTRLR1) with the number of frames in the transfer minus 1; for example, if you want to receive four data frames, write this register with 3.

Write the Baud Rate Select Register (BAUDR) to set the baud rate for the transfer.

Write the Transmit and Receive FIFO Threshold Level registers (TXFTLR and RXFTLR) respectively to set FIFO threshold levels.

Write the IMR register to set up interrupt masks.

The Slave Enable Register (SER) can be written here to enable the target slave for selection. If a slave is enabled here, the transfer begins as soon as one valid data entry is present in the transmit FIFO. If no slaves are enabled prior to writing to the Data Register (DR), the transfer does not begin until a slave is enabled.

Enable the SPI by writing 1 to the SSIENR register.

Write data for transmission to the target slave into the transmit FIFO (write DR).

If no slaves were enabled in the SER register at this point, enable it now to begin the transfer.

Poll the BUSY status to wait for the completion of the transfer. The BUSY status cannot be polled immediately.

If a transmit FIFO empty interrupt request is made, write the transmit FIFO (write DR). If a receive FIFO full interrupt request is made, read the receive FIFO (read DR).

The transfer is stopped by the shift control logic when the transmit FIFO is empty. If the transfer mode is receive only (

TMOD = 2'b10), the transfer is stopped by the shift control logic when the specified number of frames have been received. When the transfer is done, the BUSY status is reset to 0.If the transfer mode is not transmitted only (

TMOD != 01), read the receive FIFO until it is empty.Disable the SPI by writing 0 to SSIENR.

Serial-Slave Mode

SPI slave enables serial communication with master peripheral devices. When the SPI is configured as a slave device, all serial transfers are initiated and controlled by the serial bus master.

The SPI slave can only operate in transmit and receive mode. That is, TMOD field in CTRLR0 register is invalid for SPI slave. If you do not want this device to respond with data, slave output can be disabled through SLV_OE bit in CTRLR0.

When the SPI serial slave is selected during configuration, it enables its MISO data onto the serial bus. All data transfers to and from the serial slave are regulated on the serial clock line (sclk_in), driven from the serial-master device. Data are propagated from the serial slave on one edge of the serial clock line and sampled on the opposite edge.

When the SPI serial slave is not selected, it must not interfere with data transfers between the serial-master and other serial-slave devices. When the serial slave is not selected, its MISO output is buffered, resulting in a high impedance drive onto the serial master MISO line.

The serial clock that regulates the data transfer is generated by the serial-master device and input to the SPI slave on sclk_in. The slave remains in an idle state until selected by the bus master. When not actively transmitting data, the slave must hold its MISO line in a high impedance state to avoid interference with serial transfers to other slave devices. The slave continues to transfer data to and from the master device as long as it is selected.

Slave SPI Serial Transfers

If the SPI slave transmits data to the master, you must ensure that data exists in the transmit FIFO before a transfer is initiated by the serial-master device. If the master initiates a transfer to the SPI slave when no data exists in the transmit FIFO, an error flag (TXE) is set in the SPI status register, and the previously transmitted data frame is resent on MISO. For continuous data transfers, you must ensure that the transmit FIFO buffer does not become empty before all the data have been transmitted. The transmit FIFO threshold level register (TXFTLR) can be used to early interrupt (ssi_txe_intr) the processor, indicating that the transmit FIFO buffer is nearly empty. When a DMA Controller is used for APB accesses, the DMA transmit data level register (DMATDLR) can be used to early request (dma_tx_req) the DMA Controller, indicating that the transmit FIFO is nearly empty. The FIFO can then be refilled with data to continue the serial transfer.

The receive FIFO buffer should be read each time the receive FIFO generates a FIFO full interrupt request to prevent an overflow. The receive FIFO threshold level register (RXFTLR) can be used to give early indication that the receive FIFO is nearly full. When a DMA Controller is used for APB accesses, the DMA receive data level register (DMARDLR) can be used to early request (dma_rx_req) the DMA controller, indicating that the receive FIFO is nearly full.

A typical software flow for completing a continuous serial transfer from a serial master to the SPI slave is described as follows:

If the SPI slave is enabled, disable it by writing 0 to the SSI Enable register (SSIENR).

Set up the SPI control registers for the transfer. These registers can be set in any order.

Write CTRLR0 (for SPI transfers SCPH and SCPOL must be set identical to the master device).

Write TXFTLR and RXFTLR to set FIFO threshold levels.

Write the IMR register to set up interrupt masks.

Enable the SPI slave by writing 1 to SSIENR.

Write data to the data register (DR)

The SPI slave is now ready for the serial transfer. The transfer begins when the SPI slave is selected by a serial-master device.

When the transfer is underway, the BUSY status can be polled to return the transfer status. If a transmit FIFO empty interrupt request is made, write the transmit FIFO (write DR). If a receive FIFO full interrupt request is made, read the receive FIFO (read DR).

The transfer ends when the serial master removes the select input to the SPI slave. When the transfer is completed, the BUSY status is reset to 0.

Disable the SPI slave by writing 0 to SSIENR.

DMA Controller Interface

The SPI has optional built-in DMA capability which can be selected at configuration time; it has a handshaking interface to a DMA Controller to request and control transfers. The APB bus is used to perform the data transfer to or from the DMA.

The SPI uses two DMA channels, one for the transmit data and one for the received data. The SPI has these DMA registers:

DMACR: Control register to enable DMA operation.

DMATDLR: Register to set the transmit FIFO level at which a DMA request is made.

DMARDLR: Register to set the receive FIFO level at which a DMA request is made.

To enable the DMA Controller interface on the SPI, you must write the DMA Control Register (DMACR). Writing a '1' into the TDMAE bit field of DMACR enables the SPI transmit handshaking interface. Writing a '1' into the RDMAE bit field of DMACR enables the SPI receive handshaking interface.

Transmit Watermark Level and Transmit FIFO Underflow

During SPI serial transfers, transmit FIFO requests are made to the DMA Controller whenever the number of entries in the transmit FIFO is less than or equal to the DMA Transmit Data Level Register (DMATDLR) value; this is known as the watermark level. The DMA Controller responds by writing a burst of data to the transmit FIFO buffer.

Data should be fetched from the DMA often enough for the transmit FIFO to perform serial transfers continuously; that is, when the FIFO begins to empty another DMA request should be triggered. Otherwise, the FIFO will run out of data (underflow). To prevent this condition, the user must set the watermark level correctly.

Receive Watermark Level and Receive FIFO Overflow

During SPI serial transfers, receive FIFO requests are made to the DMA Controller whenever the number of entries in the receive FIFO is at or above the DMA Receive Data Level Register; that is, DMARDLR+1. This is known as the watermark level. The DMA Controller responds by fetching a burst of data from the receive FIFO buffer.

Data should be fetched by the DMA often enough for the receive FIFO to accept serial transfers continuously; that is, when the FIFO begins to fill, another DMA transfer is requested. Otherwise, the FIFO will fill with data (overflow). To prevent this condition, the user must correctly set the watermark level.

Registers

This section describes the programmable registers of the SPI. The following table provides the details of the SPI memory map. All registers in the SPI are addressed at 32-bit boundaries to remain consistent with the AHB bus. Where the physical size of any register is less than 32-bit wide, the upper unused bits of the 32-bit boundary are reserved. Writing to these bits has no effect; reading from these bits returns 0.

The base addresses of SPI are:

SPI0:

0x40124000SPI1:

0x40125000

The base addresses of SPI are:

SPI0:

0x40118000SPI1:

0x40119000

The base addresses of SPI are:

SPI0:

0x40118000SPI1:

0x40119000

The base addresses of SPI are:

SPI0:

0x40118000SPI1:

0x40119000

The base addresses of SPI are:

SPI0:

0x400E8000SPI1:

0x400E9000

The base addresses of SPI are:

SPI0:

0x40121000SPI1:

0x40122000

Name |

Address offset |

Access |

Description |

|---|---|---|---|

000h |

R/W |

This register controls the serial data transfer. It is impossible to write to this register when the SPI is enabled. The SPI is enabled and disabled by writing to the SSIENR register. |

|

004h |

R/W |

This register exists only when the SPI is configured as a master device. When the SPI is configured as a serial slave, writing to this location has no effect; reading from this location returns 0. Con trol register 1 controls the end of serial transfers when in receive-only mode. It is impossible to write to this register when the SPI is enabled. The SPI is enabled and disabled by writing to the SS IENR register. |

|

008h |

R/W |

This register enables and disables the SPI. |

|

010h |

R/W |

This register is valid only when the SPI is configured as a master device. When the SPI is configure d as a serial slave, writing to this location has no effect; reading from this location returns 0. Y ou cannot write to this register when SPI is busy. |

|

014h |

R/W |

This register is valid only when the SPI is configured as a master device. When the SPI is configure d as a serial slave, writing to this location has no effect; reading from this location returns 0. T he register derives the frequency of the serial clock that regulates the data transfer. The 16-bit field in this register defines the ssi_clk divider value. It is impossible to write to this register when the SPI is enabled. The SPI is enabled and disabled by writing to the SSIENR register. |

|

018h |

R/W |

This register controls the threshold value for the transmit FIFO memory. It is impossible to write t o this register when the SPI is enabled. The SPI is enabled and disabled by writing to the SSIENR re gister. |

|

01Ch |

R/W |

This register controls the threshold value for the receive FIFO memory. It is impossible to write to this register when the SPI is enabled. The SPI is enabled and disabled by writing to the SSIENR regi ster. |

|

020h |

R |

This register contains the number of valid data entries in the transmit FIFO memory. |

|

024h |

R |

This register contains the number of valid data entries in the receive FIFO memory. This register ca n be read at any time. |

|

028h |

R |

This is a read-only register used to indicate the current transfer status, FIFO status, and any tra nsmission/reception errors that may have occurred. The status register may be read at any time. None of the bits in this register request an interrupt. |

|

02Ch |

R/W |

This read/write register masks or enables all interrupts generated by the SPI. |

|

030h |

R |

This register reports the status of the SPI interrupts after they have been masked. |

|

034h |

R |

This read-only register reports the status of the SPI interrupts prior to masking. |

|

038h |

R |

||

03Ch |

R |

||

040h |

R |

||

044h |

R |

Serial-master : MSTICR is not used because ss_in_n is tie 1 for Motorola-SPI, ssi_mst_intr is not used. |

|

048h |

R |

||

04Ch |

R/W |

This register is only valid when SPI is configured with a set of DMA Controller interface signals. |

|

050h |

R/W |

This register is only valid when the SPI is configured with a set of DMA interface signals. |

|

054h |

R/W |

This register is only valid when SPI is configured with a set of DMA interface signals. |

|

058h |

R |

This register is present only if SPI is configured as serial-slave. |

|

05Ch |

R |

This register is present only if SPI is configured as serial-slave. |

|

060h |

R/W |

||

064h |

R/W |

||

068h |

R/W |

||

06Ch |

R/W |

||

070h |

R/W |

||

074h |

R/W |

||

078h |

R/W |

||

07Ch |

R/W |

||

080h |

R/W |

||

084h |

R/W |

||

088h |

R/W |

||

08Ch |

R/W |

||

090h |

R/W |

||

094h |

R/W |

||

098h |

R/W |

||

09Ch |

R/W |

||

0A0h |

R/W |

||

0A4h |

R/W |

||

0A8h |

R/W |

||

0ACh |

R/W |

||

0B0h |

R/W |

||

0B4h |

R/W |

||

0BCh |

R/W |

||

0C0h |

R/W |

||

0C4h |

R/W |

||

0C8h |

R/W |

||

0CCh |

R/W |

||

0D0h |

R/W |

||

0D4h |

R/W |

||

0D8h |

R/W |

||

0DCh |

R/W |

||

0E0h |

R/W |

||

0E4h |

R/W |

||

0E8h |

R/W |

||

0ECh |

R/W |

||

0F0h |

R/W |

This register is valid only when the SPI is configured as serial-master. This register controls the number of ssi_clk cycles that are delayed—from the default sample time—be fore the actual sample of the rxd input signal occurs. It is impossible to write to this register wh en the SPI is enabled; the SPI is enabled and disabled by writing to the SSIENR register. Note If this register is programmed with a value that exceeds the depth of the internal shift register s (SSI_RX_DLY_SR_DEPTH), a zero (0) delay will be applied to the rxd sample. |

|

0F4h |

R |

||

0F8h |

R |

||

0FCh |

R |

||

100h |

R |

REG_CTRLR0

Name : Control Register 0

Size : 32

Address offset : 000h

Read/write access : R/W

This register controls the serial data transfer. It is impossible to write to this register when the

SPI is enabled. The SPI is enabled and disabled by writing to the SSIENR register.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31 |

SS_T |

R/W |

0 |

When SCPH is 0 (Relevant only when the SPI is configured as a serial-master device)

|

30:25 |

RSVD |

R |

- |

Reserved |

24 |

RXBITSWAP |

R/W |

0 |

|

23 |

RXBYTESWAP |

R/W |

0 |

|

22 |

TXBITSWAP |

R/W |

0 |

|

21 |

TXBYTESWAP |

R/W |

0 |

|

20:16 |

RSVD |

R |

- |

Reserved |

15 |

CSF_EN |

R/W |

0 |

CS Force Control Enable. Relevant only when the SPI is confi gured as a serial-master device. This bit field enable SPI to force CS signal keep low until the amount of data bits (D FS * NDF) had been sent/received. SPI master will force the CS signal low even when the TX FIFO is empty during transmis sion.

|

14:11 |

RSVD |

R |

- |

Reserved |

10 |

SLV_OE |

R/W |

0 |

Slave Output Enable. Relevant only when the SPI is configure d as a serial-slave device. When configured as a serial mas ter, this bit field has no functionality. This bit enables o r disables the setting of the ssi_oe_n output from the SPI s erial slave. When SLV_OE = 1, the ssi_oe_n output can never be active. Wh en the ssi_oe_n output controls the tri-state buffer on the txd output from the slave, a high impedance state is always present on the slave txd output when SLV_OE = 1. This is useful when the master transmits in broadcast mode ( master transmits data to all slave devices). Only one slave may respond with data on the master rxd line. This bit is en abled after reset and must be disabled by software (when bro adcast mode is used), if you do not want this device to resp ond with data.

|

9:8 |

TMOD |

R/W |

00 |

Transfer Mode. Relevant only when the SPI is configured as a serial-master device. Selects the mode of transfer for seri al communication. This field does not affect the transfer du plicity. Only indicates whether the receive or transmit data are valid. In transmit-only mode, data received from the external devi ce is not valid and is not stored in the receive FIFO memory ; it is overwritten on the next transfer. In receive-only mode, transmitted data are not valid. After the first write to the transmit FIFO, the same word is retra nsmitted for the duration of the transfer. In transmit-and-receive mode, both transmit and receive da ta are valid. The transfer continues until the transmit FIFO is empty. Data received from the external device are stored into the receive FIFO memory, where it can be accessed by th e host processor.

|

7 |

SCPOL |

R/W |

0 |

Serial Clock Polarity. Valid when the frame format (FRF) is set to Motorola SPI. Used to select the polarity of the inac tive serial clock, which is held inactive when the SPI maste r is not actively transferring data on the serial bus.

|

6 |

SCPH |

R/W |

0 |

Serial Clock Phase. Valid when the frame format (FRF) is set to Motorola SPI. The serial clock phase selects the relation ship of the serial clock with the slave select signal. When SCPH = 0, data are captured on the first edge of the se rial clock. When SCPH = 1, the serial clock starts toggling one cycle after the slave select line is activated, and data are captured on the second edge of the serial clock.

|

5:4 |

FRF |

R/W |

00 |

Frame Format. Selects which serial protocol transfers the da ta.

|

3:0 |

DFS |

R/W |

0111 |

Data Frame Size. Selects the data frame length. When the dat a frame size is programmed to be less than 16 bits, the rece ive data are automatically right-justified by the receive l ogic, with the upper bits of the receive FIFO zero-padded. You must right-justify transmit data before writing into th e transmit FIFO. The transmit logic ignores the upper unused bits when transmitting the data. For the DFS decode, refer t o the following description:

|

REG_CTRLR1

Name : Control Register 1

Size : 32

Address offset : 004h

Read/write access : R/W

This register exists only when the SPI is configured as a master device. When the SPI is configured

as a serial slave, writing to this location has no effect; reading from this location returns 0. Con

trol register 1 controls the end of serial transfers when in receive-only mode. It is impossible to

write to this register when the SPI is enabled. The SPI is enabled and disabled by writing to the SS

IENR register.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:16 |

RSVD |

R |

- |

Reserved |

15:0 |

NDF |

R/W |

0x0 |

Number of Data Frames. When TMOD = 10 or TMOD = 11, this reg ister field sets the number of data frames to be continuousl y received by the SPI. The SPI continues to receive serial d ata until the number of data frames received is equal to thi s register value plus 1, which enables you to receive up to 64 KB of data in a continuous transfer. When the SPI is configured as a serial slave, the transfer c ontinues for as long as the slave is selected. Therefore, th is register serves no purpose and is not present when the SP I is configured as a serial slave. When CFS_EN is enabled, this bit field will be taken by SPI master to calculate the amount of data bits for all TMOD. |

REG_SSIENR

Name : SSI Enable Register

Size : 32

Address offset : 008h

Read/write access : R/W

This register enables and disables the SPI.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:1 |

RSVD |

R |

- |

Reserved |

0 |

SSI_EN |

R/W |

0 |

SPI Enable. Enables and disables all SPI operations. When di sabled, all serial transfers are halted immediately. Transmi t and receive FIFO buffers are cleared when the device is di sabled. It is impossible to program some of the SPI control registers when enabled. When disabled, the ssi_sleep output is set (after delay) to inform the system that it is safe to remove the ssi_clk, thus saving power consumption in the sys tem. |

REG_SER

Name : Slave Enable Register

Size : 32

Address offset : 010h

Read/write access : R/W

This register is valid only when the SPI is configured as a master device. When the SPI is configure

d as a serial slave, writing to this location has no effect; reading from this location returns 0. Y

ou cannot write to this register when SPI is busy.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:1 |

RSVD |

R |

- |

Reserved |

0 |

SER |

R/W |

0 |

Slave Select Enable Flag. When this bit is set (1), the corr esponding slave select line from the master is activated whe n a serial transfer begins. It should be noted that setting or clearing bits in this register have no effect on the corr esponding slave select outputs until a transfer is started. Before beginning a transfer, you should enable the bit in th is register that corresponds to the slave device with which the master wants to communicate.

|

REG_BAUDR

Name : Baud Rate Select

Size : 32

Address offset : 014h

Read/write access : R/W

This register is valid only when the SPI is configured as a master device. When the SPI is configure

d as a serial slave, writing to this location has no effect; reading from this location returns 0. T

he register derives the frequency of the serial clock that regulates the data transfer. The 16-bit

field in this register defines the ssi_clk divider value. It is impossible to write to this register

when the SPI is enabled. The SPI is enabled and disabled by writing to the SSIENR register.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:16 |

RSVD |

R |

- |

Reserved |

15:0 |

SCKDV |

R/W |

0x0 |

SPI Clock Divider. The LSB for this field is always set to 0 and is unaffected by a write operation, which ensures an eve n value is held in this register. If the value is 0, the ser ial output clock (sclk_out) is disabled. The frequency of th e sclk_out is derived from the equation: Fsclk_out =Fssi_cl k/SCKDV, where SCKDV is any even value between 2 and 65534. |

REG_TXFTLR

Name : Transmit FIFO Threshold Level

Size : 32

Address offset : 018h

Read/write access : R/W

This register controls the threshold value for the transmit FIFO memory. It is impossible to write t

o this register when the SPI is enabled. The SPI is enabled and disabled by writing to the SSIENR re

gister.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:6 |

RSVD |

R |

- |

Reserved |

5:0 |

TFT |

R/W |

0x0 |

Transmit FIFO Threshold. Controls the level of entries (or b elow) at which the transmit FIFO controller triggers an inte rrupt. The FIFO depth is 64; this register is sized to the n umber of address bits needed to access the FIFO. If you attempt to set this value greater than or equal to th e depth of the FIFO, this field is not written and retains i ts current value. When the number of transmit FIFO entries i s less than or equal to this value, the transmit FIFO empty interrupt is triggered. For TFT decode, refer to the followi ng description:

|

REG_RXFTLR

Name : Receive FIFO Threshold Level

Size : 32

Address offset : 01Ch

Read/write access : R/W

This register controls the threshold value for the receive FIFO memory. It is impossible to write to

this register when the SPI is enabled. The SPI is enabled and disabled by writing to the SSIENR regi

ster.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:6 |

RSVD |

R |

- |

Reserved |

5:0 |

RFT |

R/W |

0x0 |

Receive FIFO Threshold. Controls the level of entries (or ab ove) at which the receive FIFO controller triggers an interr upt. The FIFO depth is configurable in the range 2~64. This register is sized to the number of address bits needed to ac cess the FIFO. If you attempt to set this value greater than the depth of the FIFO, this field is not written and retains its current value. When the number of receive FIFO entries is greater than or e qual to this value + 1, the receive FIFO full interrupt is t riggered. For RFT decode, refer to the following description :

|

REG_TXFLR

Name : Transmit FIFO Level Register

Size : 32

Address offset : 020h

Read/write access : R

This register contains the number of valid data entries in the transmit FIFO memory.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:7 |

RSVD |

R |

- |

Reserved |

6:0 |

TXTFL |

R |

0x0 |

Transmit FIFO Level. Contains the number of valid data entri es in the transmit FIFO. |

REG_RXFLR

Name : Receive FIFO Level Register

Size : 32

Address offset : 024h

Read/write access : R

This register contains the number of valid data entries in the receive FIFO memory. This register ca

n be read at any time.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:7 |

RSVD |

R |

- |

Reserved |

6:0 |

RXTFL |

R |

0x0 |

Receive FIFO Level. Contains the number of valid data entrie s in the receive FIFO. |

REG_SR

Name : Status Register

Size : 32

Address offset : 028h

Read/write access : R

This is a read-only register used to indicate the current transfer status, FIFO status, and any tra

nsmission/reception errors that may have occurred. The status register may be read at any time. None

of the bits in this register request an interrupt.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:7 |

RSVD |

R |

- |

Reserved |

6 |

DCOL |

R |

0 |

Data Collision Error. Relevant only when the SPI is configur ed as a master device. This bit is set if the SPI master is actively transmitting when another master selects this devic e as a slave. This informs the processor that the last data transfer was halted before completion. This bit is cleared w hen read.

|

5 |

TXE |

R |

0 |

Transmission Error. Set if the transmit FIFO is empty when a transfer is started. This bit can be set only when the SPI i s configured as a slave device. Data from the previous trans mission is resent on the txd line. This bit is cleared when read.

|

4 |

RFF |

R |

0 |

Receive FIFO Full. When the receive FIFO is completely full, this bit is set. When the receive FIFO contains one or more empty location, this bit is cleared.

|

3 |

RFNE |

R |

0 |

Receive FIFO Not Empty. Set when the receive FIFO contains o ne or more entries and is cleared when the receive FIFO is e mpty. This bit can be polled by software to completely empty the receive FIFO.

|

2 |

TFE |

R |

1 |

Transmit FIFO Empty. When the transmit FIFO is completely em pty, this bit is set. When the transmit FIFO contains one or more valid entries, this bit is cleared. This bit field does not request an interrupt.

|

1 |

TFNF |

R |

1 |

Transmit FIFO Not Full. Set when the transmit FIFO contains one or more empty locations, and is cleared when the FIFO is full.

|

0 |

BUSY |

R |

0 |

SSI Busy Flag. When set, indicates that a serial transfer is in progress; when cleared indicates that the SPI is idle or disabled.

|

REG_IMR

Name : Interrupt Mask Register

Size : 32

Address offset : 02Ch

Read/write access : R/W

This read/write register masks or enables all interrupts generated by the SPI.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:8 |

RSVD |

R |

- |

Reserved |

7 |

SSRIM |

R/W |

1 |

SS_N Rising Edge Detect Interrupt Mask. This bit field is pr esent only if the SPI is configured as a serial-slave devic e.

|

6 |

TXUIM |

R/W |

1 |

Transmit FIFO Underflow Interrupt Mask. This bit field is pr esent only if the SPI is configured as a serial-slave devic e.

|

5 |

MSTIM_FAEIM |

R/W |

1 |

When SPI is configured as serial-master, this bit field is present as Multi-Master Contention Interrupt Mask.

When SPI is configured as serial-slave, this bit field is p resent as Frame Alignment Interrupt Mask.

|

4 |

RXFIM |

R/W |

1 |

Receive FIFO Full Interrupt Mask.

|

3 |

RXOIM |

R/W |

1 |

Receive FIFO Overflow Interrupt Mask.

|

2 |

RXUIM |

R/W |

1 |

Receive FIFO Underflow Interrupt Mask.

|

1 |

TXOIM |

R/W |

1 |

Transmit FIFO Overflow Interrupt Mask.

|

0 |

TXEIM |

R/W |

1 |

Transmit FIFO Empty Interrupt Mask.

|

REG_ISR

Name : Interrupt Status Register

Size : 32

Address offset : 030h

Read/write access : R

This register reports the status of the SPI interrupts after they have been masked.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:8 |

RSVD |

R |

- |

Reserved |

7 |

SSRIS |

R |

0 |

SS_N Rising Edge Detect Interrupt Status. This bit field is present only if the SPI is configured as a serial-slave dev ice.

|

6 |

TXUIS |

R |

0 |

Transmit FIFO Under Flow Interrupt Status. This bit field is present only if the SPI is configured as a serial-slave dev ice.

|

5 |

MSTIS_FAEIS |

R |

0 |

When SPI is configured as serial-master, this bit field is present as Multi-Master Contention Interrupt Status.

When SPI is configured as serial-slave, this bit field is p resent as Frame Alignment Interrupt Status.

|

4 |

RXFIS |

R |

0 |

Receive FIFO Full Interrupt Status.

|

3 |

RXOIS |

R |

0 |

Receive FIFO Overflow Interrupt Status.

|

2 |

RXUIS |

R |

0 |

Receive FIFO Underflow Interrupt Status.

|

1 |

TXOIS |

R |

0 |

Transmit FIFO Overflow Interrupt Status.

|

0 |

TXEIS |

R |

0 |

Transmit FIFO Empty Interrupt Status.

|

REG_RISR

Name : Raw Interrupt Status Register

Size : 32

Address offset : 034h

Read/write access : R

This read-only register reports the status of the SPI interrupts prior to masking.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:8 |

RSVD |

R |

- |

Reserved |

7 |

SSRIR |

R |

0 |

SS_N Rising Edge Detect Raw Interrupt Status. This bit field is present only if the SPI is configured as a serial-slave device.

|

6 |

TXUIR |

R |

0 |

Transmit FIFO Under Flow Raw Interrupt Status. This bit fiel d is present only if the SPI is configured as a serial-slav e device.

|

5 |

MSTIR_FAEIR |

R |

0 |

When SPI is configured as serial-master, this bit field is present as Multi-Master Contention Raw Interrupt Status.

When SPI is configured as serial-slave, this bit field is p resent as Frame Alignment Error Raw Interrupt Status.

|

4 |

RXFIR |

R |

0 |

Receive FIFO Full Raw Interrupt Status.

|

3 |

RXOIR |

R |

0 |

Receive FIFO Overflow Raw Interrupt Status.

|

2 |

RXUIR |

R |

0 |

Receive FIFO Underflow Raw Interrupt Status.

|

1 |

TXOIR |

R |

0 |

Transmit FIFO Overflow Raw Interrupt Status.

|

0 |

TXEIR |

R |

0 |

Transmit FIFO Empty Raw Interrupt Status.

|

REG_TXOICR

Name : Transmit FIFO Overflow Interrupt Clear Register

Size : 32

Address offset : 038h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:1 |

RSVD |

R |

- |

Reserved |

0 |

TXOICR |

R |

0 |

Clear Transmit FIFO Overflow Interrupt. This register reflec ts the status of the interrupt. A read from this register cl ears the ssi_txo_intr interrupt; writing has no effect. |

REG_RXOICR

Name : Receive FIFO Overflow Interrupt Clear Register

Size : 32

Address offset : 03Ch

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:1 |

RSVD |

R |

- |

Reserved |

0 |

RXOICR |

R |

0 |

Clear Receive FIFO Overflow Interrupt. This register reflect s the status of the interrupt. A read from this register cle ars the ssi_rxo_intr interrupt; writing has no effect. |

REG_RXUICR

Name : Receive FIFO Underflow Interrupt Clear Register

Size : 32

Address offset : 040h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:1 |

RSVD |

R |

- |

Reserved |

0 |

RXUICR |

R |

0 |

Clear Receive FIFO Underflow Interrupt. This register reflec ts the status of the interrupt. A read from this register cl ears the ssi_rxu_intr interrupt; writing has no effect. |

REG_MSTICR_FAEICR

Name : Multi-Master & Frame Alignment Error Interrupt Clear Register

Size : 32

Address offset : 044h

Read/write access : R

Serial-master : MSTICR is not used because ss_in_n is tie 1 for Motorola-SPI, ssi_mst_intr is not

used.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:1 |

RSVD |

R |

- |

Reserved |

0 |

MSTICR_FAEICR |

R |

0 |

Multi-Master Interrupt Clear Register/Frame Alignment Error Interrupt Clear Register. When SPI is configured as serial-master, this bit field is used to Clear Multi-Master Contention Interrupt. A read fro m this register clears the ssi_mst_intr interrupt; writing h as no effect. When SPI is configured as serial-slave, this bit field is u sed to Clear Frame Alignment Interrupt. A read from this reg ister clears the ssi_fae_intr interrupt; writing has no effe ct. |

REG_ICR

Name : Interrupt Clear Register

Size : 32

Address offset : 048h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:1 |

RSVD |

R |

- |

Reserved |

0 |

ICR |

R |

0 |

Clear Interrupt. This register is set if any of the interrup ts below are active. A read clears the ssi_txo_intr, ssi_rxu _intr, ssi_rxo_intr, and the ssi_mst_intr/ssi_fae_intr inter rupts. Writing to this register has no effect. |

REG_DMACR

Name : DMA Control Register

Size : 32

Address offset : 04Ch

Read/write access : R/W

This register is only valid when SPI is configured with a set of DMA Controller interface signals.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:2 |

RSVD |

R |

- |

Reserved |

1 |

TDMAE |

R/W |

0 |

Transmit DMA Enable. This bit enables/disables the transmit FIFO DMA channel.

|

0 |

RDMAE |

R/W |

0 |

Receive DMA Enable. This bit enables/disables the receive FI FO DMA channel

|

REG_DMATDLR

Name : DMA Transmit Data Level

Size : 32

Address offset : 050h

Read/write access : R/W

This register is only valid when the SPI is configured with a set of DMA interface signals.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:6 |

RSVD |

R |

- |

Reserved |

5:0 |

DMATDL |

R/W |

0x0 |

Transmit Data Level. This bit field controls the level at wh ich a DMA request is made by the transmit logic. It is equal to the watermark level; that is, the dma_tx_req signal is ge nerated when the number of valid data entries in the transmi t FIFO is equal to or below this field value, and TDMAE = 1. For DMATDL decode, refer to the following description:

|

REG_DMARDLR

Name : DMA Receive Data Level

Size : 32

Address offset : 054h

Read/write access : R/W

This register is only valid when SPI is configured with a set of DMA interface signals.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:6 |

RSVD |

R |

- |

Reserved |

5:0 |

DMARDL |

R/W |

0x0 |

Receive Data Level. This bit field controls the level at whi ch a DMA request is made by the receive logic. The watermark level = DMARDL+1; that is, dma_rx_req is generated when the number of valid data entries in the receive FIFO is equal to or above this field value + 1, and RDMAE=1. For DMARDL decod e, refer to the following description:

|

REG_TXUICR

Name : Transmit FIFO Underflow Interrupt Clear Register

Size : 32

Address offset : 058h

Read/write access : R

This register is present only if SPI is configured as serial-slave.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:1 |

RSVD |

R |

- |

Reserved |

0 |

TXUICR |

R |

0 |

When SPI is configured as serial-slave, this register is us ed to Clear Transmit FIFO Underflow Interrupt. This register reflects the status of the interrupt. A read from this regis ter clears the ssi_txu_intr interrupt; writing has no effect . |

REG_SSRICR

Name : SS_N Rising Edge Detect Interrupt Clear Register

Size : 32

Address offset : 05Ch

Read/write access : R

This register is present only if SPI is configured as serial-slave.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:1 |

RSVD |

R |

- |

Reserved |

0 |

SSRICR |

R |

0 |

When SPI is configured as serial-slave, this register is us ed to Clear SS_N Rinsing Edge Detect Interrupt. This registe r reflects the status of the interrupt. A read from this reg ister clears the ssi_ssr_intr interrupt; writing has no effe ct. |

REG_DRx

Name : Data Register x

Size : 32

Address offset : 060h + 04h * x (x=0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 34, 35)

Read/write access : R/W

The SPI data register is a 16-bit read/write buffer for the transmit/receive FIFOs. When the regist

er is read, data in the receive FIFO buffer is accessed. When it is written to, data are moved into

the transmit FIFO buffer; a write can occur only when SSI_EN = 1. FIFOs are reset when SSI_EN = 0.

Note1: If the Data Register (DR) is accessed from an AHB master (such as a DMA controller or a proce

ssor), the AHB transfer type may be a burst. During AHB burst transfers, the address increments afte

r each beat of the burst. To facilitate an AHB burst, read, or write operation to the transmit or re

ceive FIFO, the Date Register occupies thirty-six 32-bit address locations of memory map. Each of

the 16-bit address locations are aliased to the DR; single accesses to the DR may use any of the 16

-bit address locations.

Note2: The DR register in the SPI occupies thirty-six 32-bit address locations of the memory map t

o facilitate AHB burst transfers. Writing to any of these address locations has the same effect as p

ushing the data from the pwdata bus into the transmit FIFO. Reading from any of these locations has

the same effect as popping data from the receive FIFO onto the prdata bus. The FIFO buffers on the S

PI are not addressable.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:16 |

RSVD |

R |

- |

Reserved |

15:0 |

DRx |

R/W |

0x0 |

Data Register. When writing to this register, you must right -justify the data. Read data are automatically right-justi fied. Read: Receive FIFO buffer Write: Transmit FIFO buffer |

REG_RX_SAMPLE_DLY

Name : rxd Sample Delay Register

Size : 32

Address offset : 0F0h

Read/write access : R/W

This register is valid only when the SPI is configured as serial-master.

This register controls the number of ssi_clk cycles that are delayed—from the default sample time—be

fore the actual sample of the rxd input signal occurs. It is impossible to write to this register wh

en the SPI is enabled; the SPI is enabled and disabled by writing to the SSIENR register.

Note

If this register is programmed with a value that exceeds the depth of the internal shift register

s (SSI_RX_DLY_SR_DEPTH), a zero (0) delay will be applied to the rxd sample.

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:8 |

RSVD |

R |

- |

Reserved |

7:0 |

RSD |

R/W |

0x0 |

Receive Data (rxd) Sample Delay. This register is used to de lay the sample of the rxd input signal. Each value represent s a single ssi_clk delay on the sample of the rxd signal. |

REG_RSVD_0

Name : Reserved location for future use

Size : 32

Address offset : 0F4h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

RSVD |

R |

- |

Reserved |

REG_RSVD_1

Name : Reserved location for future use

Size : 32

Address offset : 0F8h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

RSVD |

R |

- |

Reserved |

REG_RSVD_2

Name : Reserved location for future use

Size : 32

Address offset : 0FCh

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:0 |

RSVD |

R |

- |

Reserved |

REG_SPI_DUMMY

Name : SPI Dummy Register

Size : 32

Address offset : 100h

Read/write access : R

Bit |

Symbol |

Access |

Reset |

Description |

|---|---|---|---|---|

31:16 |

RSVD |

R |

- |

Reserved |

15:0 |

DUMMY |

R |

0x0 |

Rsvd for hw |