# DS0900 RTL8726EA Datasheet

This document provides features and information on RTL8726EA microcontroller.

Rev. 4.6

Mar., 2025

Realtek Semiconductor Corp.

No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

Tel.: +886-3-578-0211. Fax: +886-3-577-6047

www.realtek.com

\*\*\*REALTEK

#### COPYRIGHT

© 2024 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.

#### **DISCLAIMER**

Please Read Carefully:

Realtek Semiconductor Corp., (Realtek) reserves the right to make corrections, enhancements, improvements and other changes to its products and services. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

Reproduction of significant portions in Realtek data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Realtek is not responsible or liable for such reproduced documentation. Information of third parties may be subject to additional restrictions.

Buyers and others who are developing systems that incorporate Realtek products (collectively, "Customers") understand and agree that Customers remain responsible for using their independent analysis, evaluation and judgment in designing their applications and that Customers have full and exclusive responsibility to assure the safety of Customers' applications and compliance of their applications (and of all Realtek products used in or for Customers' applications) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to their applications, Customer has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Customer agrees that prior to using or distributing any applications that include Realtek products, Customer will thoroughly test such applications and the functionality of such Realtek products as used in such applications.

Realtek's provision of technical, application or other design advice, quality characterization, reliability data or other services or information, including, but not limited to, reference designs and materials relating to evaluation kits, (collectively, "Resources") are intended to assist designers who are developing applications that incorporate Realtek products; by downloading, accessing or using Realtek's Resources in any way, Customer (individually or, if Customer is acting on behalf of a company, Customer's company) agrees to use any particular Realtek Resources solely for this purpose and subject to the terms of this Notice.

Realtek's provision of Realtek Resources does not expand or otherwise alter Realtek's applicable published warranties or warranty disclaimers for Realtek's products, and no additional obligations or liabilities arise from Realtek providing such Realtek Resources. Realtek reserves the right to make corrections, enhancements, improvements and other changes to its Realtek Resources. Realtek has not conducted any testing other than that specifically described in the published documentation for a particular Realtek Resource.

Customer is authorized to use, copy and modify any individual Realtek Resource only in connection with the development of applications that include the Realtek product(s) identified in such Realtek Resource. No other license, express or implied, by estoppel or otherwise to any other Realtek intellectual property right, and no license to any technology or intellectual property right of Realtek or any third party is granted herein, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which Realtek products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of Realtek Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from Realtek under the patents or other Realtek's intellectual property.

Realtek's Resources are provided "as is" and with all faults. Realtek disclaims all other warranties or representations, express or implied, regarding resources or use thereof, including but not limited to accuracy or completeness, title, any epidemic failure warranty and any implied warranties of merchantability, fitness for a particular purpose, and non-infringement of any third party intellectual property rights.

Realtek shall not be liable for and shall not defend or indemnify Customer against any claim, including but not limited to any infringement claim that related to or is based on any combination of products even if described in Realtek Resources or otherwise. In no event shall Realtek be liable for any actual, direct, special, collateral, indirect, punitive, incidental, consequential or exemplary damages in connection with or arising out of Realtek's Resources or use thereof, and regardless of whether Realtek has been advised of the possibility of such damages. Realtek is not responsible for any failure to meet such industry standard requirements.

Where Realtek specifically promotes products as facilitating functional safety or as compliant with industry functional safety standards, such products are intended to help enable customers to design and create their own applications that meet applicable functional safety standards and requirements. Using products in an application does not by itself establish any safety features in the application. Customers must ensure compliance with safety-related requirements and standards applicable to their applications. Designer may not use any Realtek products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death. Such equipment includes, without limitation, all medical devices identified by the U.S. FDA as Class III devices and equivalent classifications outside the U.S.

Customers agree that it has the necessary expertise to select the product with the appropriate qualification designation for their applications and that proper product selection is at Customers' own risk. Customers are solely responsible for compliance with all legal and regulatory requirements in connection with such selection.

Customer will fully indemnify Realtek and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's

RTL8726EA

non-compliance with the terms and provisions of this Notice.

#### **TRADEMARKS**

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

#### **USING THIS DOCUMENT**

This document is intended for the engineer's reference and provides detailed development information.

Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this document.

## **Contents**

| C | ontents        |                                            | 4  |

|---|----------------|--------------------------------------------|----|

| C | onventions     | 5                                          | 7  |

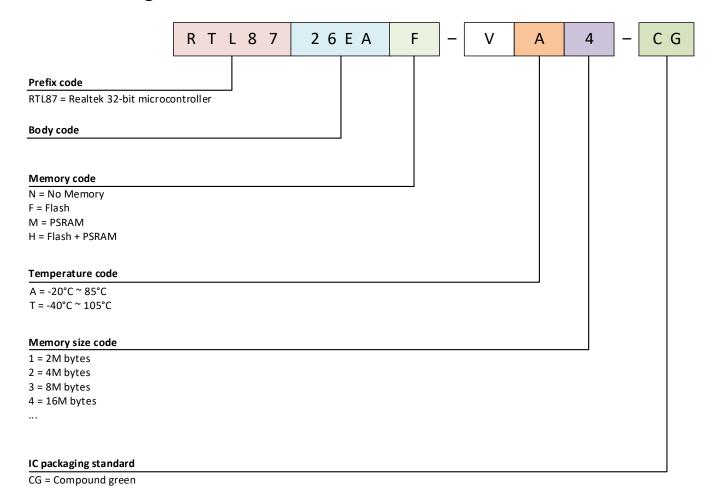

| 1 | Product        | : Overview                                 | 8  |

|   | 1.1 Ger        | neral Description                          | 8  |

|   |                | ck Diagram                                 |    |

|   |                | neral Features                             |    |

|   |                | get Applications                           |    |

|   | 1.5 Ord        | lering Information                         | 11 |

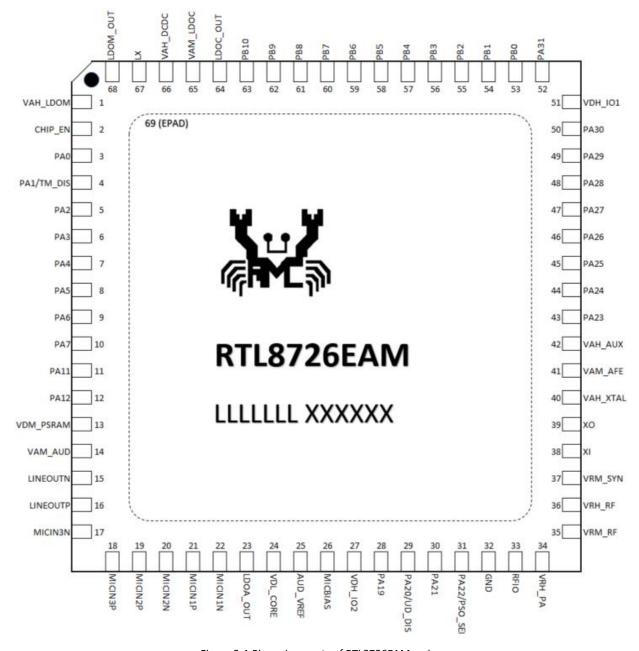

| 2 | Chip Pir       | nout Information                           | 12 |

|   | 2.1 Pin        | Assignments                                | 12 |

|   | 2.1.1          | RTL8726EAM Pinout                          |    |

|   | 2.2 Pin        | Description                                | 13 |

|   | 2.3 Alte       | ernate Functions                           | 15 |

|   | 2.4 Pov        | ver Supply for Pins                        | 15 |

| 3 | Functio        | nal Description                            | 16 |

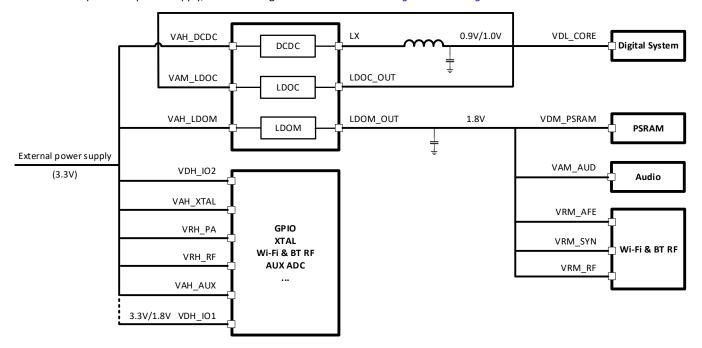

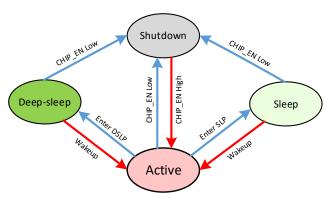

|   | 3.1 Pov        | ver Management                             | 16 |

|   | 3.1.1          | Power Structure                            |    |

|   | 3.1.2          | Power Supply Supervisor                    |    |

|   | 3.1.3          | Power Domain                               |    |

|   | 3.1.4          | Power Mode                                 | 18 |

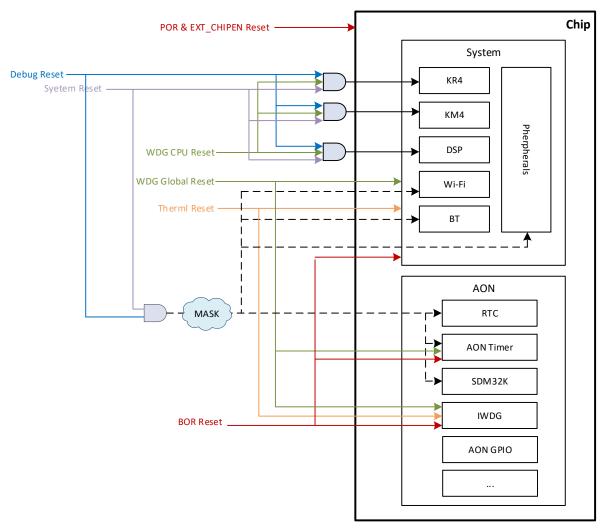

|   | 3.2 Res        | et and Clock Control (RCC)                 | 20 |

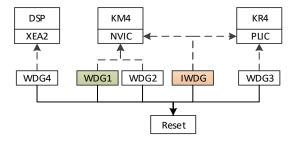

|   | 3.2.1          | Reset Control                              | 20 |

|   | 3.2.2          | Clock Control                              | 21 |

|   | 3.3 CPU        | J Architecture                             |    |

|   | 3.3.1          | KM4 Processor                              | 21 |

|   | 3.3.2          | KR4 Processor                              |    |

|   | 3.3.3          | HiFi 5 DSP                                 |    |

|   | 3.4 Me         | mory                                       |    |

|   | 3.4.1          | ROM                                        |    |

|   | 3.4.2          | SRAM                                       |    |

|   | 3.4.3          | Flash                                      |    |

|   | 3.4.4          | PSRAM                                      |    |

|   |                | Subsystem                                  |    |

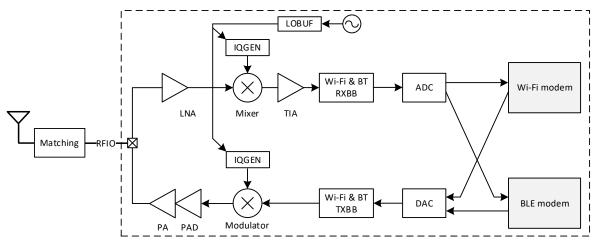

|   | 3.5.1          | RF Block Diagram                           |    |

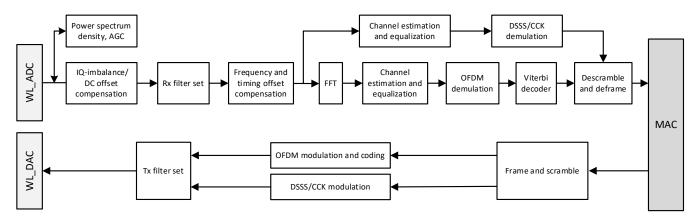

|   | 3.5.2          | WLAN                                       |    |

|   | 3.5.3          | Bluetooth                                  |    |

|   |                | AN Subsystem                               |    |

|   | 3.6.1<br>3.6.2 | WLAN Baseband                              |    |

|   |                | WLAN MACetooth Subsystem                   |    |

|   | 3.7 Blu 3.7.1  | Bluetooth Baseband                         |    |

|   | 3.7.2          | Bluetooth Link Controller                  |    |

|   | _              | urity                                      |    |

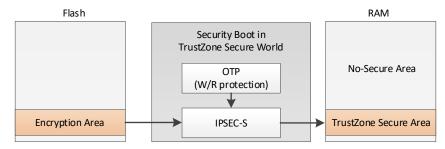

|   | 3.8.1          | Secure Boot                                |    |

|   | 3.8.2          | Elliptic Curve Signature Algorithm (ECDSA) |    |

|   | 3.8.3          | Hardware Crypto Engine (IPsec)             |    |

|   | 3.8.4          | Secure Image Protection (RSIP)             |    |

|   | 3.8.5          | Read Protection (RDP)                      |    |

|   | 3.8.6          | True Random Number Generator (TRNG)        |    |

|   |                |                                            |    |

| 3.9.1                                                                                                                          | Timers and Watchdogs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 3.3.1                                                                                                                          | Basic Timer (TIM0 ~ TIM7, TIM10 ~ TIM14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28                                                                                           |

| 3.9.2                                                                                                                          | PWM Timer (TIM8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29                                                                                           |

| 3.9.3                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.9.4                                                                                                                          | Real-time Clock (RTC) Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29                                                                                           |

| 3.9.5                                                                                                                          | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 3.9.6                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.10                                                                                                                           | Unmanned Peripheral System (UPS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| 3.11                                                                                                                           | General Direct Memory Access (GDMA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 3.12                                                                                                                           | Audio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| 3.12.                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.12.                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.12.                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.12.                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.12.                                                                                                                          | , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 3.12.                                                                                                                          | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 3.13                                                                                                                           | Inter-Processor Communication (IPC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 3.14                                                                                                                           | General-Purpose Input/Output (GPIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

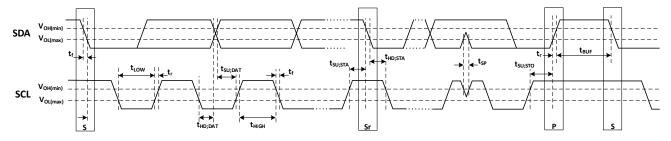

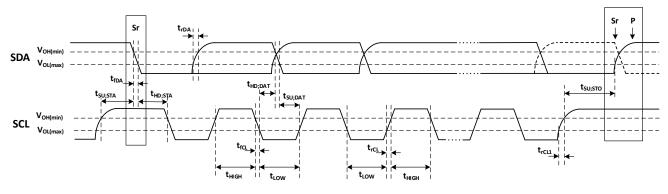

| 3.15                                                                                                                           | Inter-integrated Circuit Interface (I2C0, I2C1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

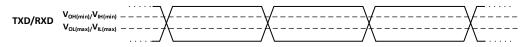

| 3.16                                                                                                                           | Universal Asynchronous Receiver/Transmitter (UARTO, UART1, UART2, UART3, LOGUART)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 3.16.                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3.16.                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

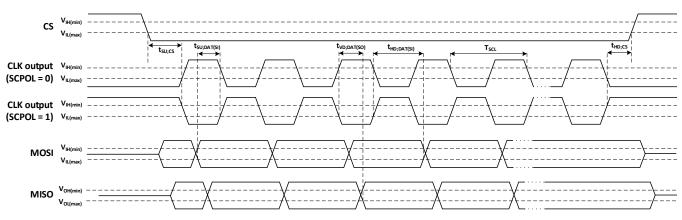

| 3.17                                                                                                                           | Serial Peripheral Interface (SPIO, SPI1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| 3.18                                                                                                                           | Light Emitting Diode Controller (LEDC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 3.19                                                                                                                           | General Analog-to-Digital Converter (ADC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 3.20                                                                                                                           | Thermal Sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 3.21                                                                                                                           | Cap-Touch Controller (CTC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36                                                                                           |

| 4 Elect                                                                                                                        | rical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                           |

|                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 4.1                                                                                                                            | Parameters Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                                           |

| 4.1.1                                                                                                                          | Maximum and Minimum Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                           |

| 4.1.2                                                                                                                          | Typical Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

|                                                                                                                                | Typical values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37                                                                                           |

| 4.1.3                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| _                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                                                                           |

| 4.2                                                                                                                            | Pin Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37<br>38                                                                                     |

| 4.2                                                                                                                            | Pin Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37<br>38<br>38                                                                               |

| 4.2                                                                                                                            | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37<br>38<br>38                                                                               |

| 4.2<br>4.3<br>4.4                                                                                                              | Pin Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

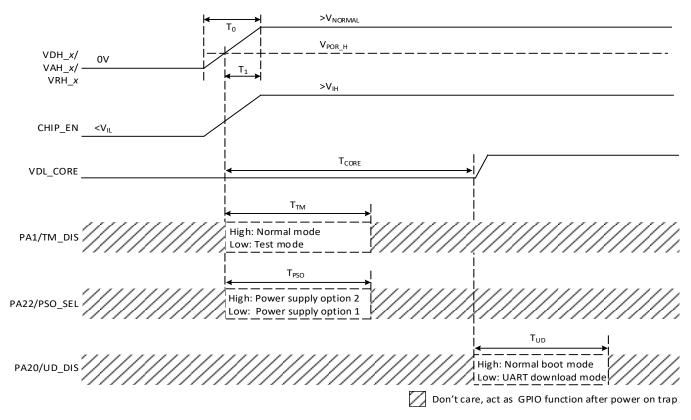

| 4.2 4.3 4.4 4.4.1                                                                                                              | Pin Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

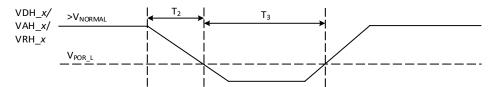

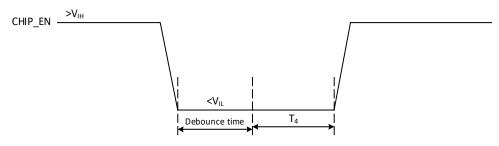

| 4.2 4.4.1<br>4.4.1<br>4.4.2<br>4.4.3                                                                                           | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35<br>38<br>38<br>38<br>39<br>39<br>40                                                       |

| 4.2 4.3 4.4.1 4.4.2 4.4.3 4.5                                                                                                  | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 4.2 4.3 4.4 4.4.1 4.4.2 4.4.3 4.5 4.6                                                                                          | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38<br>38<br>38<br>38<br>39<br>40<br>40<br>41                                                 |

| 4.2 4.3 6<br>4.4 1<br>4.4.1<br>4.4.2<br>4.4.3<br>4.5 1<br>4.6 1<br>4.7 6                                                       | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics                                                                                                                                                                                                                                                                                                                                                                                                               | 38<br>38<br>38<br>39<br>40<br>40<br>41<br>41                                                 |

| 4.2 4.3 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 4.8                                                                                      | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics                                                                                                                                                                                                                                                                                                                                                                                                               | 37<br>38<br>38<br>38<br>39<br>40<br>40<br>41<br>41                                           |

| 4.2 4.3 4.4 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 4.8 4.9                                                                              | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  // O Pin Characteristics  Power Consumption Characteristics                                                                                                                                                                                                                                                                                                                                                  | 37<br>38<br>38<br>38<br>39<br>40<br>40<br>41<br>41<br>41                                     |

| 4.2 4.3 4.4 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 4.8 4.9 4.9.1                                                                        | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  /O Pin Characteristics  Power Consumption Characteristics  Power-Saving Mode Power Consumption                                                                                                                                                                                                                                                                                                               | 37<br>38<br>38<br>38<br>39<br>40<br>40<br>41<br>41<br>41<br>42<br>42                         |

| 4.2 4.3 4.4 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 6 4.8 4.9 4.9.1 4.9.2                                                                | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  JO Pin Characteristics  Power Consumption Characteristics  Power-Saving Mode Power Consumption  MCU Operating Mode Power Consumption                                                                                                                                                                                                                                                                         | 37<br>38<br>38<br>38<br>39<br>40<br>40<br>41<br>41<br>41<br>42<br>42<br>43                   |

| 4.2 4.3 6<br>4.4 1<br>4.4.1<br>4.4.2<br>4.4.3<br>4.5 1<br>4.6 1<br>4.7 6<br>4.8 1<br>4.9 1<br>4.9.1<br>4.9.2<br>4.9.3          | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  // O Pin Characteristics  Power Consumption Characteristics  Power Saving Mode Power Consumption  MCU Operating Mode Power Consumption  RF Power Consumption                                                                                                                                                                                                                                                 | 37<br>38<br>38<br>38<br>40<br>40<br>41<br>41<br>41<br>42<br>42<br>43                         |

| 4.2 4.3 6<br>4.4 1<br>4.4.1<br>4.4.2<br>4.4.3<br>4.5 1<br>4.6 1<br>4.7 6<br>4.8 1<br>4.9.1<br>4.9.1<br>4.9.2<br>4.9.3<br>4.9.4 | Pin Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37<br>38<br>38<br>38<br>39<br>40<br>40<br>41<br>41<br>42<br>42<br>42<br>43                   |

| 4.2 4.3 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 4.8 4.9 14.9.1 4.9.2 4.9.3 4.9.4 4.9.5                                                   | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  // O Pin Characteristics  Power Consumption Characteristics  Power-Saving Mode Power Consumption  MCU Operating Mode Power Consumption  RF Power Consumption  WoWLAN Power Consumption  Bluetooth Power Consumption (TBD)                                                                                                                                                                                    | 37<br>38<br>38<br>38<br>39<br>40<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>44<br>45       |

| 4.2 4.3 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 6 4.9 1 4.9.1 4.9.2 4.9.3 4.9.4 4.9.5 4.9.6                                              | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  /O Pin Characteristics  Power Consumption Characteristics  Power-Saving Mode Power Consumption  MCU Operating Mode Power Consumption  RF Power Consumption  WOWLAN Power Consumption  Bluetooth Power Consumption (TBD)  Maximum Power Consumption                                                                                                                                                                               | 37<br>38<br>38<br>38<br>39<br>40<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>44<br>45 |

| 4.2 4.3 4.4 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 6 4.9 4.9.1 4.9.2 4.9.3 4.9.4 4.9.5 4.9.6 4.10                                       | Pin Status Absolute Maximum Ratings Operation Conditions Power Sequence Power-on Sequence Power-off Sequence CHIP_EN Reset Sequence Reset Detection Embedded Regulators Characteristics Crystal Characteristics //O Pin Characteristics Power Consumption Characteristics Power-Saving Mode Power Consumption MCU Operating Mode Power Consumption RF Power Consumption WoWLAN Power Consumption Bluetooth Power Consumption (TBD) Maximum Power Consumption RF Characteristics                                                                                                                                                        | 37 38 38 38 39 40 40 41 41 41 42 42 43 43 44 46 46                                           |

| 4.2 4.3 4.4 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 6.4 4.9 4.9.1 4.9.2 4.9.3 4.9.4 4.9.5 4.9.6 4.10 4.10.                               | Pin Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37 38 38 38 38 39 40 40 41 41 41 42 42 43 44 46 46                                           |

| 4.2 4.3 4.4 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 6.4 4.9.1 4.9.2 4.9.3 4.9.4 4.9.5 4.9.6 4.10 4.10.4.10.                              | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  // O Pin Characteristics  Power Consumption Characteristics  Power-Saving Mode Power Consumption  MCU Operating Mode Power Consumption  RF Power Consumption  WOWLAN Power Consumption  Bluetooth Power Consumption  Bluetooth Power Consumption  RF Characteristics  1 WLAN Radio Specifications  2 Bluetooth Radio Specifications                                                                                              | 37 38 38 38 38 40 40 41 41 41 42 42 43 44 45 46 46                                           |

| 4.2 4.3 4.4 4.4.1 4.4.2 4.4.3 4.5 4.6 4.7 6.4 4.9 1.4 4.9.2 4.9.3 4.9.4 4.9.5 4.9.6 4.10 4.10 4.11                             | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  /O Pin Characteristics  Power Consumption Characteristics  Power-Saving Mode Power Consumption  MCU Operating Mode Power Consumption  RF Power Consumption  WoWLAN Power Consumption  Bluetooth Power Consumption (TBD)  Maximum Power Consumption  RF Characteristics  1 WLAN Radio Specifications  2 Bluetooth Radio Specifications  Audio Characteristics                                                                     | 37 38 38 38 38 39 40 40 41 41 41 42 42 42 45 46 46 46                                        |

| 4.2                                                                                                                            | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  Power-off Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  //O Pin Characteristics  Power Consumption Characteristics  Power-Saving Mode Power Consumption  MCU Operating Mode Power Consumption  MCU Operating Mode Power Consumption  RF Power Consumption  WoWLAN Power Consumption  Bluetooth Power Consumption  Bluetooth Power Consumption  RF Characteristics  1 WLAN Radio Specifications  2 Bluetooth Radio Specifications  Audio Characteristics  1 Audio ADC | 37 38 38 38 38 39 40 40 41 41 41 42 42 42 42 43 45 46 46 46 50                               |

| 4.2                                                                                                                            | Pin Status  Absolute Maximum Ratings  Operation Conditions  Power Sequence  Power-on Sequence  CHIP_EN Reset Sequence  Reset Detection  Embedded Regulators Characteristics  Crystal Characteristics  /O Pin Characteristics  Power Consumption Characteristics  Power-Saving Mode Power Consumption  MCU Operating Mode Power Consumption  RF Power Consumption  WoWLAN Power Consumption  Bluetooth Power Consumption (TBD)  Maximum Power Consumption  RF Characteristics  1 WLAN Radio Specifications  2 Bluetooth Radio Specifications  Audio Characteristics                                                                     | 37 38 38 38 39 40 40 41 41 41 42 42 43 43 44 46 46 46 46 50 50                               |

| 4   | .13     | QSPI Flash Controller Characteristics | 51 |

|-----|---------|---------------------------------------|----|

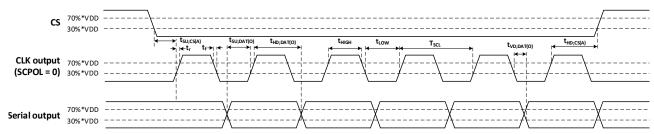

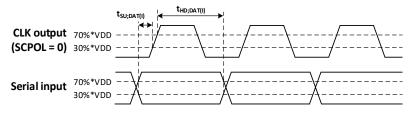

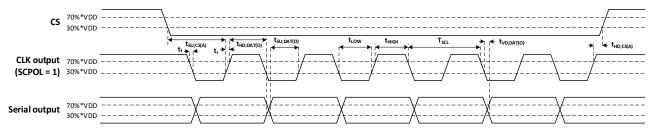

| 4   | .14     | SPI Characteristics                   | 52 |

| 4   | .15     | I2C Characteristics                   | 55 |

| 4   | .16     | UART Characteristics                  | 56 |

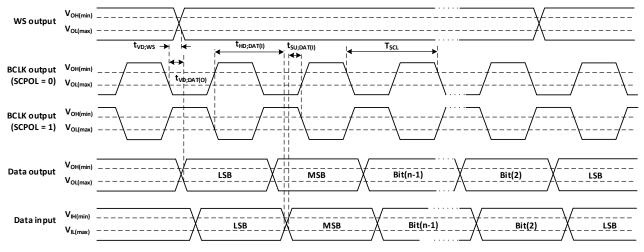

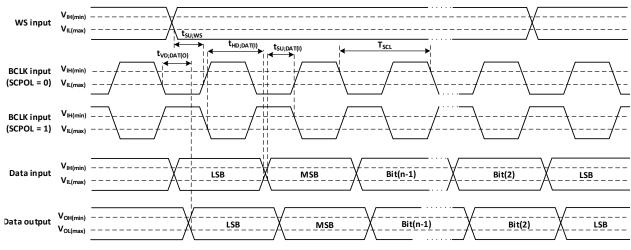

| 4   | .17     | I2S Characteristics                   | 57 |

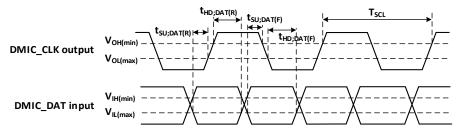

| 4   | .18     | DMIC Characteristics                  | 58 |

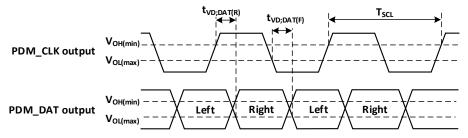

| 4   | .19     | PDM Characteristics                   | 58 |

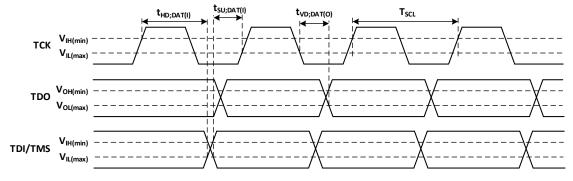

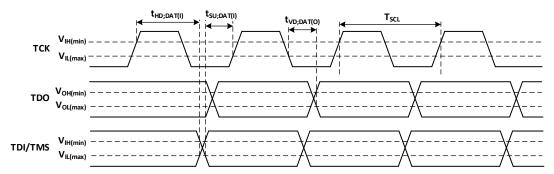

| 4   | .20     | Debug Interface Characteristics       | 59 |

|     | 4.20.1  | SWD                                   | 59 |

|     | 4.20.2  |                                       | 60 |

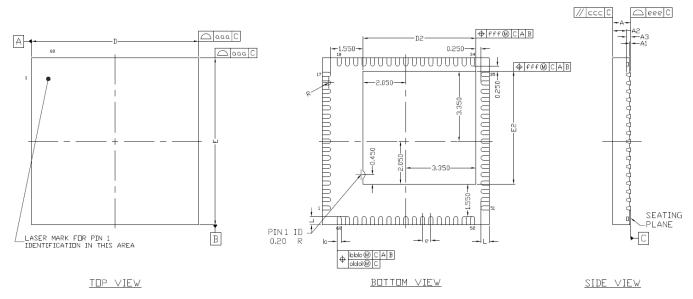

| 5   | Packa   | ge Information                        | 61 |

| 5   | .1 Q    | FN68 Package Outline                  | 61 |

| 5   | .2 Th   | nermal Characteristics                | 62 |

| Rev | ision H | istory                                | 63 |

### **Conventions**

The following abbreviations apply to indicate the MCUs of Realtek.

Real-M300 (KM4) Arm® Cortex®-M55 compatible instruction set core based on Armv8.1-M architecture, running at a frequency of up

to 400MHz.

KR4 A 32-bit processor supporting RISC-V compatible instruction set RV32IMAFC, running at a frequency of up to

400MHz.

HiFi5 DSP Cadence® Tensilica® HiFi5 DSP for audio and voice processing, running at a frequency of up to 500MHz.

AP Application Processor, designed for user application.

NP Network Processor, designed for network protocol, provides network and power management services to AP.

For most purposes, KM4 and KR4 are interchangeable. That is to say, both of them can work as AP or NP. If one of them is used as AP, the other is regarded as NP.

**¥ REALTEK** RTL8726EA

### 1 Product Overview

### 1.1 General Description

The RTL8726EA is a low-power single-chip microcontroller integrating dual RISC cores (Arm® Cortex®-M55 compatible instruction set and RISC-V compatible instruction set) and a digital signal processor (Cadence® Tensilica® HiFi 5 DSP). It is designed for optimized power efficiency, RF performance, and reduced audio transmission latency. It also encompasses the characteristics of low-power chip, including fine-grained clock gating, multiple power modes, and dynamic power scaling.

The KM4 (also called Real-M300) is a 3-staged pipelined 32-bit processor based on Armv8.1-M architecture supporting Cortex-M55 compatible instruction set, running at a frequency of up to 400MHz. It offers system enhancements such as enhanced debug features, single-precision floating-point unit (FPU), Digital Signal Processing (DSP) extension, TrustZone-M security for hardware-enforced isolation, and a high level of support block integration.

The KR4 is a 32-bit processor that supports RISC-V compatible instruction set RV32IMAFC, running at a frequency of up to 400MHz. RISC-V is a standard free and open instruction set architecture (ISA) based on RISC, delivering a new level of free, extensible software and hardware freedom on architecture.

The Cadence Tensilica HiFi 5 DSP is a high-performance embedded DSP optimized for high-performance front-end, far-field and near-field audio and voice processing, running at a frequency of up to 500MHz. It is also designed for enabling efficient implementations of neural network (NN) based speech recognition algorithms. The HiFi 5 DSP is a five-slot VLIW machine which can execute up to eight 32x32-bit MACs per cycle. It can issue two 128-bit loads per cycle, or one load and one store of 128-bit per cycle for parallel loads and stores of the operand and results. The HiFi 5 DSP offers additional floating-point precision support through an optional Single Precision vector floating-point unit (SP FPU), which can perform up to eight single-precision floating-point MACs per cycle. For supporting neural network-based speech recognition algorithms, the HiFi 5 DSP provides Neural Network Extension option which enables the hardware to perform up to thirty-two 8x16, 4x16 and 8x8-bit MACs per cycle.

The RTL8726EA integrates the latest specifications of Wi-Fi (Wi-Fi 6) and Bluetooth (Bluetooth 5.2). It supports 802.11 b/g/n/ax wireless LAN (WLAN) network at 2.4GHz with 20MHz bandwidth. It consists of WLAN MAC, a 1T1R capable WLAN baseband, RF, and Bluetooth, providing complete Wi-Fi and Bluetooth functionalities.

A variety of peripheral interfaces, including UART, SPI, I2C, LEDC, etc., as well as sensor controllers (such as ADC, Cap-Touch, and thermal) are integrated into RTL8726EA. Besides, the RTL8726EA has rich audio features for smart audio applications with dedicated microphone interfaces (AMIC/DMIC), built-in voice activity detection (VAD), acoustic echo cancellation (AEC) reference ADC, mono audio DAC, and I2S. Abundant general-purpose I/O (GPIOs) can be configured to different functions according to different secure IoT (Internet of Things) applications flexibly. The user-friendly development kits (SDK and HDK) are provided to customers for developing applications.

The RTL8726EA also incorporates high-speed memories with on-chip SRAM and stacked Flash or PSRAM. A dedicated SPI Flash controller provides a flexible and efficient way to access NOR Flash (e.g., byte and block access). A multilayer AXI bus interconnect supports internal and external memory access.

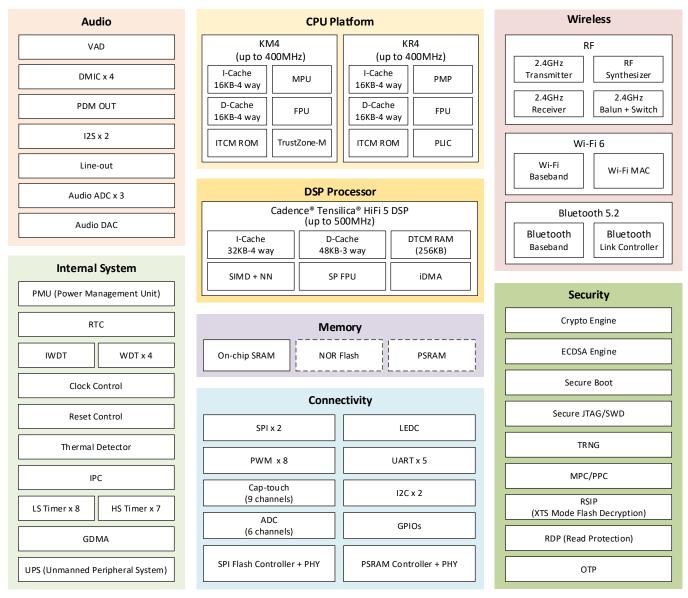

### 1.2 Block Diagram

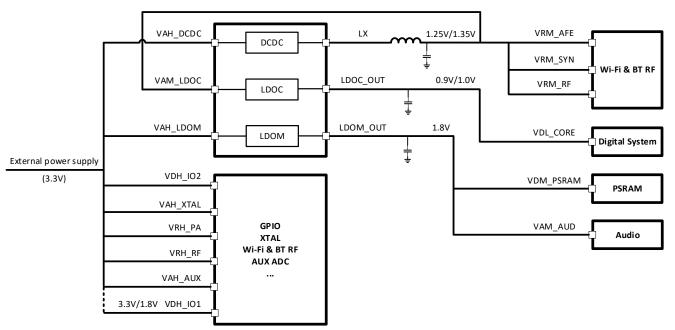

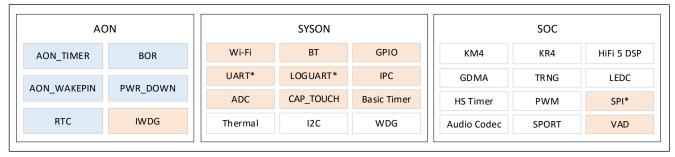

The functional block diagram is shown in *Figure 1-1*. This diagram provides a view of the chip's major functional components and core complexes.

Figure 1-1 Block diagram

#### 1.3 General Features

Table 1-1 General features

| Item            | Features                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of Cores | 3                                                                                                                                                                                                                                                                                                                                                                      |

| KM4 Processor   | <ul> <li>Arm Cortex-M55 compatible instruction set</li> <li>I-Cache: 16K bytes</li> <li>D-Cache: 16K bytes</li> <li>Running at a frequency of up to 400MHz</li> <li>Memory Protection Unit (MPU) with up to 16 regions per security state</li> <li>Built-in Nested Vectored Interrupt Controller (NVIC)</li> <li>Single-precision floating point unit (FPU)</li> </ul> |

| KR4 Processor   | <ul> <li>SWD with 8 instruction breakpoints and 1 data watchpoint</li> <li>RISC-V compatible instruction set</li> <li>I-Cache: 16K bytes</li> <li>D-Cache: 16K bytes</li> <li>Running at a frequency of up to 400MHz</li> <li>Single-precision floating point unit (FPU)</li> </ul>                                                                                    |

|                      | Platform-Level Interrupt Controller (PLIC)                                                                                    |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                      | Physical Memory Protection (PMP) with up to 16 regions                                                                        |

|                      | Supports 8 trigger points                                                                                                     |

| DCD Drasassar        | Cadence Tensilica HiFi 5 DSP                                                                                                  |

| DSP Processor        |                                                                                                                               |

|                      | I-Cache: 32K bytes                                                                                                            |

|                      | D-Cache: 48K bytes                                                                                                            |

|                      | DTCM RAM: 256K bytes                                                                                                          |

|                      | Running at a frequency of up to 500MHz                                                                                        |

|                      | • 5 slot VLIW engine                                                                                                          |

|                      | • 128 bit SIMD support                                                                                                        |

|                      | Two 128-bit loads store units                                                                                                 |

|                      | Fixed-point MACs per cycle                                                                                                    |

|                      | ■ 32bit x 32bit: up to 8                                                                                                      |

|                      | ■ 24bit x 24bit: up to 8                                                                                                      |

|                      | ■ 32bit x 16bit: up to 16                                                                                                     |

|                      | ■ 16bit x 16bit: up to 16                                                                                                     |

|                      | ■ 16bit x 8bit, 8bit x 8bit, 16bit x 4bit through special NN engine: up to 32                                                 |

|                      | <ul> <li>Up to 8 single-precision floating-point MACs per cycle</li> </ul>                                                    |

| Memory Supported     | On-chip SRAM                                                                                                                  |

|                      | PSARM (optional)                                                                                                              |

|                      | NOR Flash (optional)                                                                                                          |

| WLAN                 | • 2.4GHz Wi-Fi 6 (802.11 b/g/n/ax), 1x1                                                                                       |

|                      | • Tx power (2.4G):                                                                                                            |

|                      | ■ 11b 11Mbps: 20dBm                                                                                                           |

|                      | ■ 11g 54Mbps: 19dBm (EVM< −25dB)                                                                                              |

|                      | ■ 11n MCS7-HT20: 18dBm (EVM< −27dB)                                                                                           |

|                      | ■ 11ax MCS9-HE20: 16dBm (EVM< −32dB)                                                                                          |

|                      | • Rx sensitivity (2.4G):                                                                                                      |

|                      | ■ 11b 11Mbps: −91dBm                                                                                                          |

|                      | ■ 11g 54Mbps: −78dBm                                                                                                          |

|                      | ■ 11n MCS7-HT20: −76.5dBm                                                                                                     |

|                      | ■ 11ax MCS9-HE20: -70.5dBm                                                                                                    |

| Bluetooth            | Bluetooth 5.2 specification compliant, dual mode:                                                                             |

| Biuetootii           | ■ Bluetooth Basic Rate/Enhanced Data Rate (BR/EDR)                                                                            |

|                      |                                                                                                                               |

|                      | Bluetooth Low Energy (BLE)                                                                                                    |

|                      | Supports both 500kbps and 125kbps LE-Coded PHY (long range)     Supports seatter not (consurrent control and peripheral mode) |

|                      | Supports scatter-net (concurrent central and peripheral mode)     Supports SIG Mark v. 1.0 and v. 1.4.                        |

|                      | • Supports SIG Mesh v1.0 and v1.1                                                                                             |

|                      | AoA and AoD (both connection-oriented and connectionless)      O( to the O(S and D(S)))                                       |

|                      | ISO (both CIS and BIS)                                                                                                        |

| RF                   | Supports antenna diversity                                                                                                    |

| Audio                | Built-in a low-energy Voice Activity Detection (VAD)                                                                          |

|                      | Up to 128KB VAD buffer                                                                                                        |

|                      | • 3-channel Audio ADC, SNR > 98dB A-weighted and THD+N < -80dB                                                                |

|                      | <ul><li>Mono DAC, SNR &gt; 100dB A-weighted and THD+N &lt; -85dB</li></ul>                                                    |

|                      | PDM interface function for external speaker AMP                                                                               |

|                      | 4-channel digital microphone interface supported                                                                              |

|                      | • 12S x 2                                                                                                                     |

|                      | <ul> <li>Supports up to 8-channel I2S transmitter and receiver by TDM or PCM mode</li> </ul>                                  |

|                      | <ul> <li>Up to 4 serial data outputs/inputs are transmitted within a sample period</li> </ul>                                 |

| Serial Communication | ● 12C x 2                                                                                                                     |

|                      | • UART x 5                                                                                                                    |

|                      | • SPI x 2                                                                                                                     |

| Package              | QFN68, 8mm x 8mm, 0.4mm pitch                                                                                                 |

| - ackage             | Q. 1000, Chilli A Chillin, C. Thillin Pitch                                                                                   |

### 1.4 Target Applications

With dual RISC cores running up to 400MHz, enhanced computing capability, stable security performance and abundant peripheral resources, the RTL8726EA series is widely used in various fields, such as:

- Smart home appliance

- Line controller

- BLE gateway

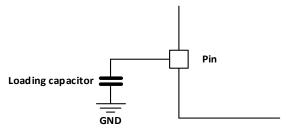

- Micro inverter