芯片信息

Introduction

本spec主要说明和定义用于在不同阶段标识chip的信息,包括CP/FT阶段的生产记录信息,feature set和封装相关信息,内部使用以及开放给客户使用的chip 编号以及版本号。这些信息用于生产端问题的追溯,客户或内部软件区分不同chip进行不同配置。

下面分类别介绍这些信息的定义,以及记录和使用方式。

生产记录信息

生产记录信息记录于OTP/Efuse隐藏区中,在CP/FT量产阶段由机台烧录,用于记录die坐标以及特定生产过程,供后续生产过程或者RMA分析过程追溯使用。使用时由机台或者软件读取。记录的信息如下表格:

OTP byte address |

Bit map |

Name |

Description |

|---|---|---|---|

0x7F2 |

[2:0] |

HVS |

0x7F2[2:0] : HVS (High V Stress) (it should be proceeded below 28 nm) 111:High V Stress is proceeded 000: High V Stress is not proceeded yet. Others: Invalid |

[7:3] |

RSVD |

0x7F2[7:3] : RSVD (For future use) |

|

0x7F3 |

[1:0] |

PFID |

0x7F3[1:0] PFID 11: not pass 00: pass Others: Invalid |

[3:2] |

RSVD |

0x7F3[3:2] reserved for ATE golden sample flag |

|

[7:5] |

RSVD |

0x7F3[7:5] RSVD |

|

0x7F4 |

[7:0] |

UUID |

0x7F4[7:0] :coordinate X |

0x7F5 |

[7:0] |

0x7F5[7:0] :coordinate Y |

|

0x7F6 |

[7:0] |

0x7F6[4:0] : wafer刻號 0x7F6[7:5] : CRC[2:0] |

|

0x7F7 |

[7:0] |

0x7F7[7:0] : CRC[10:3] |

如下具体解释各个栏位含义和用法:

1,HVS:记录chip是否进行过高压测试。CP测试需要对core device进行1.38V高压测试,排除早夭chip。HVS栏位用于记录是否进行过高压测试,在CP烧写。记录目的为避免重复测试。HVS 有3 bit,应测试工程师要求,冗余的2 bit用于防止烧写出错。使用时会进行3bit同时烧写。量产测试检查时若发现HVS 3个bit不全为相同的值,会丢弃此chip。

2,PFID:记录FT测试完成后是否通过。在FT完成最后步骤烧写。应测试工程师要求,冗余的1 bit用于防止烧写出错。使用时会进行2bit同时烧写,量产测试检查时若发现PFID 2个bit不全为相同的值,会丢弃此chip。

3,UUID:包括5-bit wafer 刻号,以及die在wafer上的x/y坐标各8 bits。为防止烧写过程出错,以及保证后续追溯时内容的准确性,UUID也包括对wafer刻号以及x/y坐标三项信息进行的11-bit CRC值。UUID在CP阶段进行烧写。

如下通过例子介绍UUID的记录内容和CRC计算方式:

參數 |

10進制 |

2進制 |

bit數 |

|---|---|---|---|

x軸座標 |

255 |

1111 1111 |

8 bits |

y軸座標 |

255 |

1111 1111 |

8 bits |

wafer刻號 |

25 |

1 1001 |

5 bits |

CRC |

1072 |

100 0011 0000 |

11 bits |

CRC計算方法如下:

Step1~5 皆為十進制運算

Step1: TEMP1= x 座標*10^5 + y座標*10^2 + wafer 刻號

假設wafer#25, (x,y)=(255,255),則 TEMP1=25525525

Step 2: TEMP2=TEMP1*10000

TEMP2=255255250000

Step 3: TEMP3=mod(TEMP2,2039)

TEMP3= 968

Step 4: CRC= (2039+1) – TEMP3

CRC= 1072

Step 5: UUID = TEMP2 + CRC

UUID = 255255251072

下面是check wafer information CRC是否正确的计算公式:

read UUID= x 座標*10^9 + y座標*10^6 + wafer 刻號*10^4 + CRC

UUID=255255251072

mod(UUID,2039)若為1,則PASS

Mode(255255251072, 2039)=1, pass

在应用中,也需要有CHIP有一个唯一ID (所有的chip个体的ID都不相同) 供客户使用。客户通常把这个ID用作序列号(例如USB字符序列号或者其他的终端应用),或者用来作为产生密码和随机数的seed。UUID还做不到,要再加入RT lot number(非FAB的lot number),lot number是5个符号的序列号,每个符号有字母A~Z加数字0~9,共36种可能,所以每个符号需要6 bit 表示,共需要增加5*6 = 30 bit记录lot number。我们定义按0~9,A~Z的顺序对应6 bit的0~35.

为不改变原本UUID CRC计算规则,lot number 未计入CRC计算。

OTP byte address |

Bit map |

Name |

Description |

|---|---|---|---|

N |

[7:0] |

LOT NUM |

[5:0]: 5th lot number[5:0] [7:6]: 4th lot number[1:0] For example: if lot number is "L8CM6", the 5th lot number[5:0]=0x6 the 4th lot number[5:0]=0x16 the 3rd lot number[5:0]=0xC the 2nd lot number[5:0]=0x8 the 1st lot number[5:0]=0x15 |

N+1 |

[7:0] |

[3:0]: 4th lot number[5:2] [7:4]: 3rd lot number[3:0] |

|

N+2 |

[7:0] |

[1:0]: 3rd lot number[5:4] [7:2]: 2nd lot number[5:0] |

|

N+3 |

[7:0] |

[5:0]: 1st lot number[5:0] [7:6]: reserved |

Re-mark信息

Re-mark信息记录在OTP隐藏区中,FT生产时可以根据市场需求烧写不同re-mark值,使得在相同封装下可以得到不同型号的chip,这些不同型号的chip有不同feature特性。Re-mark信息用于限制部分功能或性能,这种限制有基于市场价格策略故意为之,也有因为chip生产品质无法达到最高performance。

Re-mark信息由CPU 软件读取,读取后软件通过对相应内部寄存器设定使得Re-mark 信息生效,达到限制功能或性能的目的。

为了便于将来生产时不同型号的产品可以根据市场出货情况进行库存调节,即将经过FT测试后的一个型号chip再次Re-mark成另外的型号,Re-mark信息都多留了一倍的冗余bit,使得每个Re-mark信息bit可以被改写两次。

由于Re-mark信息记录在OTP的区域未经过保护,理论上客户是可以通过冗余bit的烧写,让原本限制的功能恢复的。但PM认为没有必要花代价进行这样的保护,因为我们会告知客户未宣称的功能和性能在产测时未测试,正规的客户不敢使用我们宣称产测未保证的功能。(后续产品会考虑通过密码保护隐藏区写的功能起到一定保护的作用)

根据市场需求,Re-mark信息包括如下内容:

CPU Core number:根据产品定位需求,定义内部A32 core 的数量为0~2个。

CPU Clock rate: 因制程差异A32的最高可操作频率可能会有差异,根据量产时测得的频率表现区分不同等级的产品。CPU Clock rate 分几个档位记录A32最高可操作频率。当然也允许因为市场需求将高等级产品Re-mark成低等级出货。

WIFI Single band/dual band support:根据产品定位需求,定义是否支持WIFI 5G band

802.11 protocol:根据产品定位需求,定义是否支持802.11ax

memory size: 根据产品定位需求,定义是否限制内部KGD memory size的大小到原始实际size的一半。

如下表格是Re-mark信息在OTP中具体的排布和bit 定义:

N |

[3:0] |

re-mark info (需进行xor 运算) |

[3:0] :CPU Core number 令: A= bit[1] xor bit[3], B= bit[0] xor bit[2], if: AB = 2'b 00 : A32*2; AB = 2'b 01 : A32*1; AB = 2'b 10 : A32*0; AB = 2'b 11 : RSVD; |

[7:4] |

[7:4] :CPU Clock rate(A32) 令: C= bit[5] xor bit[7], D= bit[4] xor bit[6], if: CD = 2'b 00 : 1.4GHz CD = 2'b 01 : 1.2GHz CD = 2'b 10 : 1GHz; CD = 2'b 11 : 800MHz; |

||

N+1 |

[1:0] |

[1:0] :wifi Single band/dual band support if: Bit[1] xor Bit[0] = 1'b 0: dual band: 2.4G+ 5G Bit[1] xor Bit[0] = 1'b 1: single band: 2.4G (如下PG值与XOR计算结果对应) 2'b 11: dual band: 2.4G+ 5G 2'b 00: dual band: 2.4G+ 5G 2'b 10: single band: 2.4G 2'b 01: single band: 2.4G |

|

[3:2] |

[3:2] :802.11 protocol if: Bit[3] xor Bit[2] = 1'b 0: 11ax Bit[3] xor Bit[2] = 1'b 1: 11n only (如下PG值与XOR计算结果对应) 2'b 11: 11ax 2'b 00: 11ax 2'b 10: 11n only 2'b 01: 11n only |

||

[5:4] |

[5:4] : memory size if: Bit[5] xor Bit[4] = 1'b 0: original size Bit[5] xor Bit[4] = 1'b 1: reduce size to half 目前预计用到的封装是内置512Mbit DDR2 KGD时,可能会被remark成256Mbit |

||

[7:6] |

[7:6] : RSVD (For future use) |

||

N+2 |

[7:0] |

[7:0] : RSVD (For future use) |

|

N+3 |

[7:0] |

RSVD |

[7:0] : RSVD (For future use) |

封装信息

封装信息记录在OTP隐藏区中。封装信息以package number形式记录。package number是5 bit的流水号,每个package number代表一个封装形式+内部除了主芯片外的KGD/ component型号的组合。每个package number对应到一个或者多个Bonding 线图号。

不是所有bonding线图号都对应package number,只有确定产出的bonding 图号才会分配package number。SD在封装作业完成后给软件使用前给对应的bonding线图号分配package number。当软件需要区分线图内部KGD信息或者需要区分因package内容不同造成的型号差异时,需分配不同的package number。

Package number需要结合RTL_NO+RTL_VER使用,每一个RTL_NO+RTL_VER的组合对应一组从0开始计数的Package number流水号。如RTL8730E-VA1 中Package number = 0对应的线图和RTL8730E-VA2 中Package number = 0的线图可能是不一样的。

package number 原本用内部bonding 线图号代替最直观,但公司的Bonding线图号的表示方式是:RL Number+ Bonding number,如RL6678-BD1001。线图号需要结合RL number一起才能确定对应一个封装设计。因为按公司的规则,线图号是在特定RL number下的流水号,相同流水号在不同RL number下是不同的封装设计。封装信息需要被release给客户的软件代码使用,为了避免客户在获取封装信息时用到不想让客户看到的内部RL number,改为用上述package number记录。使用时,需要额外的表格记录package number和 bonding 线图号的对应关系,以及和封装形式+内部除了主芯片外的KGD型号的对应关系。

封装信息由内部CPU软件读取使用。软件会根据封装信息得到内部除主芯片外其他KGD信息(Flash, DDR, PSRAM等)以及封装出pin信息,以此进行正确配置以及结合其他信息得到芯片具体型号。

为了防止出现内部KGD或者其他bonding option更改后但又不希望SDK改动的情况出现,以及在其他package number相同的情况下,增加3-bit internal sub number来区分记录真实的封装号。给客户使用的程序代码只会读取5-bit package number,3-bit internal sub number只在内部追溯时供软件读取结合Package Number获取真实封装信息。internal sub number 从0开始计数,每当出现多于1个BD number对应到一个package number时internal sub number加1。

RL6678/RL6842由于leadframe工期问题,做了临时工程批的BD number,这个临时工程批和后来的正式BD number就用这个sub number区分。

相同设计会更换不同封装厂会有不同BD number,不同封装厂的BD number用sub number区分。

如下是封装信息记录在OTP中的排布和具体定义:

N |

[4:0] |

Package Number |

[4:0]: package number: (1) package number: 封装流水号0~31。 (2) Package MCM的DDR/psram信息需要对照bonding number获取; (3) BD number与package number的对应list由SD维护。 Example: [7:5] [4:0] BD number package information 0 0 RL6678-BD1001 QFN88 + DDR2_512M W975116NG + NOR_256M W25Q256JVWIB1 0 1 RL6678-BD1002 QFN88 + PSRAM_64M APS6408L + NOR_64M GD25Q64EDIG 0 2 RL6678-BD1003 QFN144+DDR2_1G W971G16NG + NAND_1G GD5F1GQ5UEDIG-RT 0 3 RL6678-BD1004 QFN228 single chip 1 1 RL6678-BD1005 QFN88 + PSRAM_64M W956D8MKY + NOR_64M W25Q64JVW … |

[7:5] |

Internal sub Number |

[7:5]: Internal sub Number 0~7 用于区分在相同package number情况下真实的bonding图号信息。不开放给客户使用。从0开始计数。 举例见Package Number 栏位说明 |

Chip ID and Chip version

Chip ID and version for customer

给客户用到的版本号包括RTL_NO,CHIP_VER, ES_FLAG信息。除了RTL_NO, 这些信息都记录在OTP中。预期在CP或者FT中烧写。RTL_NO(RTL number)不用记录,这个信息是此芯片产品的系列名,由于特定的一包软件代码不需要同时支持多个系列的产品,只对应到特定的一个系列产品,因此RTL_NO 就不用记录,需要读取该信息的软件程序预先知道。

给客户看到的CHIP ID,即在datasheet中ordering information的产品型号信息,会由此版本号再加上package信息以及re-mark信息一起得到。请参考后续具体描述。ES_FLAG, CHIP_VER信息由软件读取使用。

ES_FLAG由1 bit表示。用于标识此chip是否是Engineer sample。Engineer sample的定义是未经完全的量产测试,可能只是进行了实验室测试,在开发早期给客户使用的工程样品。Engineer sample包括MPW的chip,也包括量产版本chip在量产前期未经量产测试给客户的sample。ES_FLAG在量产时由CP或FT烧写成0,在给客户Engineer sample阶段由lab "烧写"成1.

记录Engineer Sample版本的目的主要是为了方便追溯未量产测试chip的问题。原本也可以用于软件根据版本判断区分内部不同MPW版次,经过讨论认为Engineer sample阶段和量产阶段的软件可能不会考虑兼容性,会是不同的SDK,没有必要区分版本信息,因此不再区分Engineer Sample 的版本,而只标识是否是Engineer Sample。

CHIP_VER由5 bit表示,表示release给客户看到的此型号芯片的版次,CHIP_VER=0,表示第一版。能让客户看到的改版,不论是ECO还是换FAB厂,都会让CHIP_VER进版加一。绝大部分情况下,此CHIP_VER是和实际IC改版一致的,当RL number不变化时也是和chip的RL version是一致的。但当IC发生隐性置换时,即不让客户知道我们发生了改版时,此处的CHIP_VER不会修改。当chip发生RL number的修改时,CHIP_VER会在之前的基础上加1,此时和RL version 记录的号码会不一样。CHIP_VER 预期在CP或者FT中烧写。

CHIP_VER和软件使用CHIP_VER 的API一般不开放给客户,只有当客户明确知道我们有改版,且希望知道我们判断版本的方式时才release。而RL number + RL Version是真实记录chip版本,且一定不release给客户的内容,这是为了在有隐性置换时能让我们有方法知道真实的chip 版本。

n |

[4:0] |

CHIP Version for Customer |

[4:0]: CHIP_VER chip Version number. Record the chip Version. Counting start from 0. 0,1, 2, 3 … map to version 0(A),1(B),2(C),3(D) … |

[5] |

CHIP Version for Customer |

[5]: ES_FLAG 0: MP chip 1: Engineer Sample |

|

[7:6] |

RSVD |

RSVD |

Chip ID and version for internal use

RL_NO 和RL_VER记录内部工程ID号和实际版本信息,用于内部追溯和根据真实版本信息进行初始配置,此信息预期不会release给客户。由于会发生改版后不会告知客户隐性置换的情况,实际版本信息和给客户看到的版本信息会不同,而通常配置和patch跟实际版本信息有关,所以需要内部软件能够获取此真实信息。RL_NO 和RL_VER存放在寄存器中,由内部CPU软件读取使用。

RL_NO用来记录RL/RLE number,有16 bit位宽,以16 bit hex格式读出的4个数字表示。如chip RL6678,其RL_NO = 0x6678.

RL_VER用来记录RL/RLE version,有4 bit位宽,从0开始计数,0表示RL/RLE version的A版。此次版本号为0

小心

为了不让客户容易的看到此信息,需要做到:

1,RL_NO 和RL_VER 寄存器的内容不能被显示的读到。用CHIP_INFO_EN register来屏蔽RL_NO 和RL_VER的内容使客户不能直接读到此版本信息。

2,内部软件操作此RL_NO 和RL_VER 寄存器的源代码不能release给客户。

RL_VER为了ECO改版时的便利,需要做到任何一层metal都可以改变版本信息,这样可以减少ECO改版改变的metal层数,节省成本。RL_NO 不需要做这样的设计,因为RL_NO修改意味着是全新的投片,任何层的ECO没有额外的代价。另外,在改版中,经常遇到只改ROM code的场景,ROM code的修改只用改VIA层,不会改到metal,所以为了考虑这种情况,需要让ROM code用到的VIA层也可以更改RL_VER信息。这需要在芯片电路中定制一个独立的hard block IP实现。目前有实现将16-bit RL_NO和4-bit RL_VER做在一个独立的IP里面。

Chip整合需要注意此IP满足CPU读取需求时有供电,CPU可能有比较底层的patch需要根据芯片版本进行,此IP需要比较基础的供电。

使用Chip Information

根据软件或量产所需查询的内容使用场景, 总结如下表格:

软件查询内容 |

所需读取的索引信息 |

所需表格 |

|---|---|---|

公开的封装和内部KGD信息 |

RTL_NO(可不读取) + CHIP_VER + Package Number |

型号配置对应表 |

公开的芯片型号 |

RTL_NO(可不读取) + CHIP_VER + Package Number + Re-mark info |

型号配置对应表 |

公开的芯片版本 |

CHIP_VER + ES_FLAG |

None |

芯片内部版本 |

RL_NO + RL_VER |

None |

芯片内部真实料号组合 |

RL_NO + RL_VER + Package Number + Internal sub number |

型号配置对应表 |

假设前提:

1,认为换fab厂一定可以改RL_NO 和RL_VER

2.公开的软件只用公开的CHIP_VER 进行版本区分和配置。

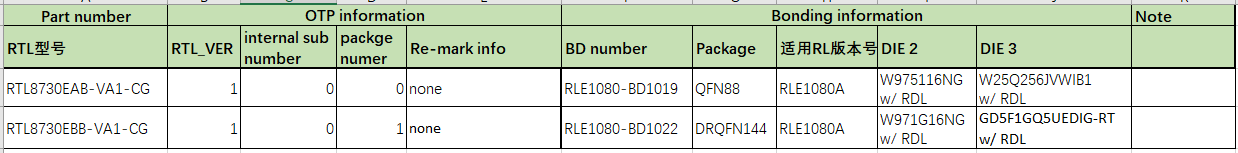

型号配置对应表示例:

Registers

Register Memory Map

Name |

Address Offset |

Access |

Description |

|---|---|---|---|

Internal chip information Registers |

|||

CHIP_INFO |

0x0000 |

R/W |

Record the internal chip information |

Registers and Field Description

Internal chip information Registers

CHIP_INFO

Name: chip information register

Size: 32 bits

Address offset: 0x0000

Read/write access: read/write

Bit |

Name |

Access |

Reset |

Description |

|---|---|---|---|---|

31:28 |

CHIP_INFO_EN |

RW |

0 |

Enable Internal Chip Information display. 0xA: enable. Others: disable. Note: CHIP_INFO can be read only if CHIP_INFO_EN[3:0]=0xA, otherwise the read result will return 0x0. |

27:20 |

RESERVED |

RO |

0 |

RESERVED |

19:16 |

RL_VER |

RO |

0 |

Internal Chip version. It records the actual chip version and cannot be publicly used. 0x0-0xF: character ‘A’ - ‘P’ |

15:0 |

RL_NO |

RO |

0x6678 |

RL or RLE number. It cannot be publicly used. |